# Running a TMS320C64x+ Codec Across TMS320C64x+ Based DSP Platforms

Prasad, Keshava

#### ABSTRACT

This application report describes the device differences to be taken care for running the C64x+<sup>™</sup> video codec software on different C64x+ based platforms. This document assumes that the codec software is developed for the C64x+ digital signal processor (DSP) core. As many TI platforms have a C64x+ DSP, this document gives the details for running the standalone codec software on a C64x+ platform. This document also assumes that the enhanced direct memory access (EDMA3) is available in the system-on-chip (SoC) for data transfers. The devices considered in this document are TMS320DM6446, TMS320DM647/DM648, TMS320DM6437, TMS320DM6467 and OMAP3530, all of which have TMS320C64x+<sup>™</sup> DSP cores.

All of the documentation mentioned in this application report are referenced in Section 4 of this document.

|   | Contents                                   |   |

|---|--------------------------------------------|---|

| 1 | Introduction                               | 1 |

| 2 | Background                                 | 2 |

| 3 | Device Differences to Be Considered        | 2 |

| 1 | References                                 | 6 |

|   | List of Figures                            |   |

| 1 | Codec Package                              | 2 |

| 2 | Setting the Device Configuration for L1/L2 |   |

| 3 | Linker Command File                        | 4 |

|   | List of Tables                             |   |

| 1 | L1 and L2 Memory Sizes                     | 3 |

| 2 | L1 and L2 Memory Base Addresses            | 4 |

|   |                                            |   |

####

# 1 Introduction

# 1.1 Purpose and Scope

Typically, a C64x+ codec is developed and validated on a specific platform (e.g., DM6446). However, this codec can be used on another platform having a C64x+ DSP. This document explains the architectural details to consider before running it on a different platform.

The scope of this document is only for the codec software that runs on the C64x+ DSP.

C64x+, TMS320C64x+, Code Composer Studio are trademarks of Texas Instruments. All other trademarks are the property of their respective owners.

#### 1.2 Assumptions

It is assumed in this document that the codec has been implemented on a C64x+ DSP platform and runs on a given C64x+ SoC. To illustrate the changes that need to be done for running on different SoC's, an example codec MPEG4 Encoder is used. This is typically applicable to any video codec that is implemented on the C64x+ DSP and does not assume any hardware accelerators. Also, this is mainly to run a standalone codec and needs Code Composer Studio<sup>™</sup> software along with the simulator/emulator for the specific platform.

# 1.3 Target Audience

All individuals involved in the development of video and image application software on the C64x+ DSP platforms. This is also very handy for field application engineers running a C64x+ library on different C64x+ platforms.

# 2 Background

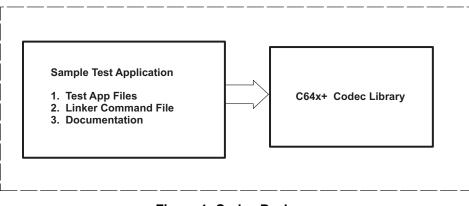

Figure 1 shows the basic codec package, which has a codec library that contains sample test application, user's guide, data sheet, etc. The codec library considered here is a C64x+ library. The codec is developed and validated on a specific platform having C64x+ DSP core (this information is included in the release notes). The codec's are supplied with a standalone package or real-time software components (RTSC) package. The standalone package has a sample application that contains the Code Composer Studio Project and sample test files, which are configured to run on a specific platform. For the RTSC package, the sample app is included in the app folder (e.g, for MPEG4 encoder, the sample app is available at packages\ti\sdo\codecs\mpeg4enc\app folder).

Figure 1. Codec Package

Ideally, the C64x+ library can be used for any platform having a C64x+ DSP. But sometimes, there will be changes required in the library/test application to make it run on a given C64x+ based platform depending on the device. The following section describes the SoC features that need to be considered before running the codec on a given C64x+ platform. The sample application needs SoC details that are discussed below so that it can run on an EVM or software development platform (SDP) that has C64x+ DSP.

# 3 Device Differences to Be Considered

# 3.1 L1 and L2 Memory Considerations

The video performance sensitive data (like macro block data) is often executed from L1 or L2 memories. This memory is requested by the codec through the IALG interface. The algAlloc function returns the request for memory type of IALG\_DARAMO with a specified size through a memTab [memory table], The application needs to allocate this on-chip memory (L1/L2). L1 memory is preferable due to performance reasons, if the required size is available in L1. For the given SoC, the L1 and L2 memory sizes is important to understand.

www.ti.com

For performance reasons, the C64x+ video codec designs assume a specific configuration for L1D RAM size. If this is not fulfilled for a given SoC (i.e., the SoC does not have the required L1/L2 memories specified in the codec data sheet), it may still be possible to run the codec by allocating this memory in some other memory space (e.g., allocating it in L2 SRAM or DDR if I2 is not sufficient). This makes sure that the codec is functional, but the performance of the codec might need to be benchmarked with this change, since the performance might drop due to increased latencies.

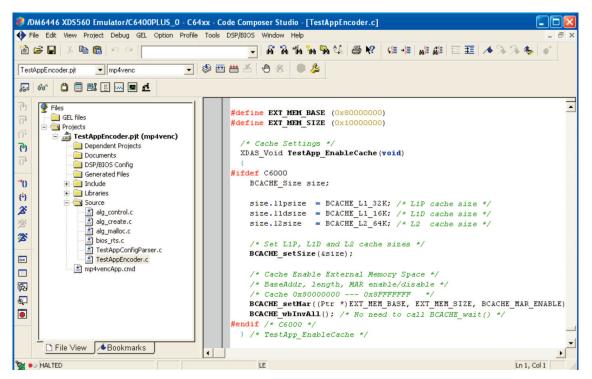

The data sheet of a codec mentions the memory requirements and the assumptions based on which performance (L1/L2 sizes, clock frequencies, etc.) of the codec is measured and the platform on which the performance was benchmarked. The sample application has a function that configures the L1/L2 cache and RAM sizes. Figure 2 shows the snapshot of this function.

Figure 2. Setting the Device Configuration for L1/L2

Table 1 gives the L1/L2 memory sizes for the different platforms considered in this document.

Table 1. L1 and L2 Memory Sizes

|          | DM6446                                        | DM6437                                      | DM648                                       | DM647                                       | DM6467                                      | OMAP3530                                      |

|----------|-----------------------------------------------|---------------------------------------------|---------------------------------------------|---------------------------------------------|---------------------------------------------|-----------------------------------------------|

| L1D Size | 80K-Byte L1D<br>Data<br>RAM/Cache             | 80K-Byte L1D<br>Data RAM/Cache              | 32K-Byte L1D<br>Data RAM/Cache              | 32K-Byte L1D<br>Data RAM/Cache              | 32K-Byte L1D<br>Data RAM/Cache              | 80K-Byte L1D<br>Data<br>RAM/Cache             |

| L2 Size  | 64K-Byte L2<br>Unified<br>Mapped<br>RAM/Cache | 128K-Byte L2<br>Unified Mapped<br>RAM/Cache | 512K-Byte L2<br>Unified Mapped<br>RAM/Cache | 256K-Byte L2<br>Unified Mapped<br>RAM/Cache | 128K-Byte L2<br>Unified Mapped<br>RAM/Cache | 64K-Byte L2<br>Unified<br>Mapped<br>RAM/Cache |

Note that except for DM6446, DM6437 and OMAP3530, other devices have L1D memory of just 32KB. Taking the example of the MPEG4 Encoder, the C64x+ MPEG4 Encoder needs 52KB of L1D RAM. If we need to run this in DM6467, which has just 32KB of L1D RAM, we need to use L2 RAM instead. DM6437/DM6446 can be configured to have 64KB of internal memory, so the L1D memory is not an issue for these platforms.

Note that this might have some performance implications (placing the data in L2 instead of L1), so the performance benchmarking needs to be done with this change in memory.

So, if the L1/L2 configuration is different from what is expected by the codec (as per the data sheet), then there is no change required in the library, only the L1/L2 configuration need to be changed in the test application.

#### 3.2 L1/L2 Base addresses

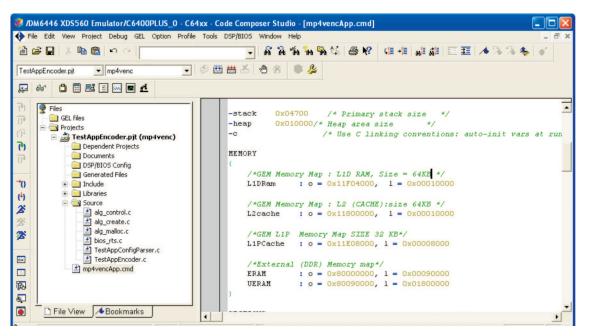

The memory map of the platform could be different. To run the codec, the memory map needs to be provided for linking, through the linker command file. Figure 3 is a snapshot of the linker command file that is provided with the standalone sample application.

Figure 3. Linker Command File

The L1 and L2 base addresses can vary from one SoC to another; to run a codec on a given SoC, you need to know the start addresses of the memories. This information is summarized in Table 2.

|                     | DM6446      | DM6437      | DM648       | DM6467      | OMAP3530    |

|---------------------|-------------|-------------|-------------|-------------|-------------|

| L1D base<br>address | 0x11F0 4000 | 0x10F0 4000 | 0x00F0 0000 | 0x11F0 0000 | 0x10F0 4000 |

| L2 base address     | 0x1180 0000 | 0x1080 0000 | 0x00A0 0000 | 0x1181 8000 | 0x1080 0000 |

If the memory map is different, there is no change required in the library, only the L1/L2 addresses need to be changed in the test application linker command file.

### 3.3 EDMA features: TC's and QDMA Base Address

The MPEG4 encoder uses QDMA for all data transfers. QDMA requires many register settings for configuring transfers. The EDMA configuration base address varies for different platforms.

The base addresses for different platforms under consideration are provided in Table 3.

#### Table 3. EDMA Features

|                          | DM6446      | DM6437      | DM648       | DM6467      | OMAP3530    |

|--------------------------|-------------|-------------|-------------|-------------|-------------|

| QDMA config base address | 0x01C0 0000 | 0x01C0 0000 | 0x02A0 0000 | 0x01C0 0000 | 0x01C0 0000 |

| Number of TC's           | 2           | 3           | 4           | 4           | 2           |

4 Running a TMS320C64x+ Codec Across TMS320C64x+ Based DSP Platforms

SPRAB73–September 2009 Submit Documentation Feedback

|                         | Table 3. EDMA Features (continued) |        |       |        |          |

|-------------------------|------------------------------------|--------|-------|--------|----------|

|                         | DM6446                             | DM6437 | DM648 | DM6467 | OMAP3530 |

| Number of QDMA channels | 8                                  | 8      | 8     | 8      | 8        |

Also, the number of transfer controllers (TC's) could be different. Table 3 also gives the TC's for different SoC's.

At present, the QDMA base address is chosen during build time, so if there is a change in the config base address (e.g., DM6446 to DM648) then the codec library needs to be rebuilt. It is possible to abstract this using the framework, (e.g., by defining the resource manager API's to take care of the EDMA base address), but such a framework is not available in some of the legacy codecs.

Another factor that affects the system performance is the number of TC's. This may not affect the standalone codec performance in the presence of other system traffic; but in the presence of other system traffic, the number of TC's can affect the overall performance of the system.

The number of QDMA channels available in these SoC's is 8. This is the upper bound on the channel usage for the codec (e.g., MPEG4 encoder uses 4 QDMA channels).

# 3.4 DDR Base Address

Due to differences in the memory maps, the DDR base address can change across platforms. This is needed for memory allocation for data and code. In Figure 2, the linker command file specifies the DDR base address sections. This need to be updated based on the SoC's memory map. Table 4 gives the address for the SoC's under consideration.

### Table 4. DDR Base addresses

|             | DM6446      | DM6437      | DM648       | DM6467      | OMAP3530    |

|-------------|-------------|-------------|-------------|-------------|-------------|

| DDR Address | 0x8000 0000 | 0x8000 0000 | 0xE000 0000 | 0x8000 0000 | 0x8000 0000 |

If the DDR address is different, then there is no change required in the library; only the test application linker command file needs to be updated with the correct address.

### 3.5 Other Aspects

In addition to the architectural specifics explained above, there are some other compatibility aspects that need to be considered before running the codec. Some examples are given below that are very specific to the SoC; some can have software workarounds.

### 3.5.1 Color Formats

The DM6446 platform supports YUV 422ILE format, but the YUV format supported in DM6467 is YUV 420 semi planar. The MPEG4 encoder on C64x+ supports YUV420 planar and YUV422ILE. To run this on DM6467, some format conversion are needed. Similarly, the native colour format for DM648 is YUV 422 planar.

### 3.5.2 Performance

The performance or the maximum resolution possible on a given platform depends on the clock frequency of the DSP, the L1/L2 configurations, the EMIF/DDR bandwidth available, etc. Even though taking care of the device aspects makes the codec functional on a given platform, the performance has to be benchmarked separately.

www.ti.com

References

## 4 References

- TMS320DM6467 Digital Media System-on-Chip Data Manual (SPRS403)

- TMS320DM6437 Digital Media Processor Data Manual (SPRS345)

- TMS320DM6446 Digital Media System-on-Chip Data Manual (SPRS283)

- TMS320DM647/TMS320DM648 Digital Media Processor Data Manual (SPRS372)

- OMAP3530/25 Applications Processor Data Manual (SPRS507)

#### **IMPORTANT NOTICE**

Texas Instruments Incorporated and its subsidiaries (TI) reserve the right to make corrections, modifications, enhancements, improvements, and other changes to its products and services at any time and to discontinue any product or service without notice. Customers should obtain the latest relevant information before placing orders and should verify that such information is current and complete. All products are sold subject to TI's terms and conditions of sale supplied at the time of order acknowledgment.

TI warrants performance of its hardware products to the specifications applicable at the time of sale in accordance with TI's standard warranty. Testing and other quality control techniques are used to the extent TI deems necessary to support this warranty. Except where mandated by government requirements, testing of all parameters of each product is not necessarily performed.

TI assumes no liability for applications assistance or customer product design. Customers are responsible for their products and applications using TI components. To minimize the risks associated with customer products and applications, customers should provide adequate design and operating safeguards.

TI does not warrant or represent that any license, either express or implied, is granted under any TI patent right, copyright, mask work right, or other TI intellectual property right relating to any combination, machine, or process in which TI products or services are used. Information published by TI regarding third-party products or services does not constitute a license from TI to use such products or services or a warranty or endorsement thereof. Use of such information may require a license from a third party under the patents or other intellectual property of the third party, or a license from TI under the patents or other intellectual property of TI.

Reproduction of TI information in TI data books or data sheets is permissible only if reproduction is without alteration and is accompanied by all associated warranties, conditions, limitations, and notices. Reproduction of this information with alteration is an unfair and deceptive business practice. TI is not responsible or liable for such altered documentation. Information of third parties may be subject to additional restrictions.

Resale of TI products or services with statements different from or beyond the parameters stated by TI for that product or service voids all express and any implied warranties for the associated TI product or service and is an unfair and deceptive business practice. TI is not responsible or liable for any such statements.

TI products are not authorized for use in safety-critical applications (such as life support) where a failure of the TI product would reasonably be expected to cause severe personal injury or death, unless officers of the parties have executed an agreement specifically governing such use. Buyers represent that they have all necessary expertise in the safety and regulatory ramifications of their applications, and acknowledge and agree that they are solely responsible for all legal, regulatory and safety-related requirements concerning their products and any use of TI products in such safety-critical applications, notwithstanding any applications-related information or support that may be provided by TI. Further, Buyers must fully indemnify TI and its representatives against any damages arising out of the use of TI products in such safety-critical applications.

TI products are neither designed nor intended for use in military/aerospace applications or environments unless the TI products are specifically designated by TI as military-grade or "enhanced plastic." Only products designated by TI as military-grade meet military specifications. Buyers acknowledge and agree that any such use of TI products which TI has not designated as military-grade is solely at the Buyer's risk, and that they are solely responsible for compliance with all legal and regulatory requirements in connection with such use.

TI products are neither designed nor intended for use in automotive applications or environments unless the specific TI products are designated by TI as compliant with ISO/TS 16949 requirements. Buyers acknowledge and agree that, if they use any non-designated products in automotive applications, TI will not be responsible for any failure to meet such requirements.

Following are URLs where you can obtain information on other Texas Instruments products and application solutions:

| Products                    |                        | Applications       |                           |

|-----------------------------|------------------------|--------------------|---------------------------|

| Amplifiers                  | amplifier.ti.com       | Audio              | www.ti.com/audio          |

| Data Converters             | dataconverter.ti.com   | Automotive         | www.ti.com/automotive     |

| DLP® Products               | www.dlp.com            | Broadband          | www.ti.com/broadband      |

| DSP                         | dsp.ti.com             | Digital Control    | www.ti.com/digitalcontrol |

| Clocks and Timers           | www.ti.com/clocks      | Medical            | www.ti.com/medical        |

| Interface                   | interface.ti.com       | Military           | www.ti.com/military       |

| Logic                       | logic.ti.com           | Optical Networking | www.ti.com/opticalnetwork |

| Power Mgmt                  | power.ti.com           | Security           | www.ti.com/security       |

| Microcontrollers            | microcontroller.ti.com | Telephony          | www.ti.com/telephony      |

| RFID                        | www.ti-rfid.com        | Video & Imaging    | www.ti.com/video          |

| RF/IF and ZigBee® Solutions | www.ti.com/lprf        | Wireless           | www.ti.com/wireless       |

Mailing Address: Texas Instruments, Post Office Box 655303, Dallas, Texas 75265 Copyright © 2009, Texas Instruments Incorporated