Sahil Deshpande and Hareesh Janakiraman

#### C2000 Microcontrollers

### ABSTRACT

C2000 Real-time MCUs feature three types of Controller Area Network (CAN) modules: eCAN, DCAN and MCAN. While eCAN and DCAN only support classic CAN, MCAN supports both classic CAN and CAN FD. Devices such as TMS320F2838xD, TMS320F2838xS, TMS320F28003x and TMS320F280015x feature both DCAN and MCAN modules. Some C2000 devices only feature the MCAN module since it supports both classic CAN and CAN FD. Although all of the aforementioned CAN modules are compliant with the CAN protocol standard, none of them are software-compatible with each other. Specifically, the DCAN and MCAN module employ a completely different architecture and hence, register and bit structure. This warrants a very different programming approach between the modules. This document is intended to ease the migration from DCAN to the MCAN module. It discusses the most common operations such as module initialization, bit-timing configuration, message RAM configuration, buffer and FIFO configuration, data transmission, reception (with filtering) and error handling. It explains how these operations are done in DCAN and MCAN modules. Code snippets are shown as warranted.

## **Table of Contents**

| 1 Introduction                                   |    |

|--------------------------------------------------|----|

| 2 Key Differences Between DCAN and MCAN          | 2  |

| 3 Module Initialization                          | 2  |

| 3.1 DCAN Initialization                          | 3  |

| 3.2 MCAN Initialization                          | 3  |

| 3.3 Initialization sequence                      | 3  |

| 3.4 Code Snippets for Module Initialization      | 4  |

| 4 Bit Timing Configuration                       | 7  |

| 5 Message RAM Configuration                      | 9  |

| 6 Interrupt handling                             | 11 |

| 6.1 MCAN Interrupt Sources                       | 11 |

| 6.2 DCAN Interrupt Handling                      | 12 |

| 6.3 MCAN Interrupt Handling                      | 15 |

| 7 Transmitting data                              |    |

| 7.1 Basic Transmission Process                   |    |

| 7.2 MCAN Vs DCAN Transmit Procedural Differences | 17 |

| 7.3 MCAN Transmit Concepts                       | 18 |

| 8 Receiving Data                                 | 21 |

| 8.1 Introduction to Reception                    |    |

| 8.2 Basic Reception Process                      |    |

| 8.3 Filter Elements                              |    |

| 8.4 Rx Buffer                                    | 25 |

| 8.5 Rx FIFO                                      | 26 |

| 8.6 Receiving High Priority Messages             |    |

| 9 Avoiding network errors                        |    |

| 10 References                                    | 28 |

## Trademarks

All trademarks are the property of their respective owners.

1

# 1 Introduction

On any given device, C2000 MCUs have typically featured only one type of CAN module. For example, either eCAN or DCAN. When MCAN was introduced in the C2000 family, some MCUs featured both DCAN and MCAN. This necessitated the user to understand and program two completely different types of CAN modules. To eliminate this hardship, MCAN has been chosen as the CAN platform moving forward, since MCAN supports both classic CAN as well as CAN FD. This document lists the primary differences between the DCAN and MCAN modules. It then proceeds to highlight how common operations are done in both modules.

To determine which CAN module is featured in a given C2000 MCU, see C2000 Real-time Control MCU Peripherals Guide.

# 2 Key Differences Between DCAN and MCAN

CAN FD offers two significant advantages over classic CAN:

- Faster bit-rate in the data-phase, increasing the overall throughput. An application can choose to transmit the entire frame at the same bit-rate by setting *CCCR.BRSE* = 0. This way, the application still takes advantage of the higher payload capability of CAN FD.

- Higher payload size (up to 64 bytes) compared to classic CAN (up to 8 bytes), reducing protocol overhead.

Note that the physical-layer requirements in terms of transceiver, bus termination and so forth is identical between Classic CAN and CAN FD. If higher bit-rates are desired for the data phase in CAN FD, then transceivers designed for such bit-rates must be used.

Table 2-1 highlights the key differences between the DCAN and MCAN modules from a usage and programming perspective.

| Feature                                                    | DCAN                                                                                                                         | MCAN                                                                                           |

|------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------|

| Bit-rate                                                   | Fixed bit-rate for the entire frame       Two bit-rates can be used: a slow for the nominal phase and a faste the data phase |                                                                                                |

| Transmission speed                                         | Capped at 1Mbps                                                                                                              | Up to 1Mbps can be used for the <i>nominal phase</i> and up to 5Mbps for the <i>data phase</i> |

| Number of bytes transmitted per frame (Payload capability) | Any number of bytes from 0 to 8 can be transmitted                                                                           | In addition to 0 to 8 bytes, transmission of 12/16/20/24/32/48/64 data bytes is possible       |

| Nomenclature of data storage elements                      | Data is stored in Message Objects. Message objects are also sometimes referred to as Mailboxes.                              | Data is stored in buffers tied to <i>filter elements</i>                                       |

| Number of data storage elements                            | Fixed at 32, regardless of the number of bytes to be transmitted or received                                                 | Depending on the configuration of the element, the number of buffers is flexible               |

| CRC-field length                                           | 15 bits                                                                                                                      | 15, 17 or 21-bit CRC                                                                           |

| Time-stamping support                                      | No                                                                                                                           | Yes                                                                                            |

| Transmitter delay compensation                             | Not required                                                                                                                 | Required for faster bit-rates in the data phase                                                |

## Table 2-1. DCAN and MCAN Feature Differences

# 3 Module Initialization

The first few initialization steps are identical for both DCAN and MCAN modules. The initialization mode is entered either by software (setting the *CAN\_CTL.INIT* and *MCAN\_CCCR.INIT* bits, respectively), by a hardware reset, by going to a bus-off state or in the case of MCAN, on the detection of an uncorrected bit error in the Message RAM. In this state, the message transfer is stopped, the CANTX output is driven recessive (high) and the error counters remain unchanged. Setting the *INIT* bit does not change any configuration registers.

To complete the software initialization, the *INIT* bit can be reset, and after an occurrence of a sequence of 11 recessive bits (Bus-idle state), communication can commence.

The step-by-step process for module initialization is shown below for each module.

## **3.1 DCAN Initialization**

- 1. Initialize Message RAM

- 2. Configure bit-timing

- 3. Configure Message Objects (optional → can also be done after initialization and while module is operational).

## 3.2 MCAN Initialization

- 1. Configure Message RAM (See Section 5).

- 2. Configure CAN mode (Classic CAN or CAN FD).

- 3. Configure bit-timing (See Section 4).

- 4. Configure bit-rate switching (enable or disable).

- 5. Configure Filter Elements (optional  $\rightarrow$  can also be done after initialization and while module is operational).

Note that the status registers related to Tx/Rx are reset on switching to init mode in MCAN.

## 3.3 Initialization sequence

The individual steps for initialization of DCAN and MCAN modules, along with the key differences have been listed in Table 3-1:

| Operation                                                                                         | DCAN                       | MCAN                                                                                                                                                                                     |  |

|---------------------------------------------------------------------------------------------------|----------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| Enter Initialization Mode                                                                         | Set CAN_CTL.INIT bit       | Set <i>MCAN_CCCR.INIT</i> bit and check that the bit has been set                                                                                                                        |  |

| Unlock Protected Registers                                                                        | Set CAN_CTL.CCE bit        | Set MCAN_CCCR.CCE bit                                                                                                                                                                    |  |

| Configure CAN Mode and Bit Rate Switching                                                         | Not applicable             | Set <i>MCAN_CCCR.FDOE</i> bit for CAN FD<br>function<br>Set <i>MCAN_CCCR.BRSE</i> bit to enable Bit<br>Rate Switching (BRS)<br>(Both bits need to be 0 for Classic CAN<br>Communication) |  |

| Configure bit-timing                                                                              | Configure CAN_BTR register | Configure MCAN_NBTP register                                                                                                                                                             |  |

| Configure data bit-timing                                                                         | Not applicable             | Configure <i>MCAN_DBTP</i> register (Not needed for Classic CAN as BRS is disabled)                                                                                                      |  |

| Message RAM Configuration                                                                         | Not applicable             | See Message RAM configuration                                                                                                                                                            |  |

| Global Filter Configuration, if required (determines how the module handles non-matching frames). | Not applicable             | Set MCAN_GFC Register                                                                                                                                                                    |  |

| Receive and Transmit Configuration (can be done at run time as well)                              | Setup Message Object       | Filter Configuration                                                                                                                                                                     |  |

| Lock Protected Registers                                                                          | Clear CAN_CTL.CCE bit      | Clear MCAN_CCCR.CCE bit                                                                                                                                                                  |  |

| Return module to normal operation                                                                 | Clear CAN_CTL.INIT bit     | Clear MCAN_CCCR.INIT bit                                                                                                                                                                 |  |

### Table 3-1. DCAN/MCAN Initialization Sequence

In addition to the steps shown above, for MCAN, the MCAN Clock Divider may need to be set up as part of the initialization process. This configuration is typically done via the AUXCLKDIVSEL register (refer to the device-specific TRM to determine the register for clock division). For 120 MHz and 200 MHz devices, *C2000ware* examples configure the MCAN bit-clock to 40 MHz. If an application desires a smaller time quanta (TQ), other configurations for the bit-clock are possible. However, the parameters for the Nominal and Data Bit Timings need to be changed accordingly. Figure 3-1 shows the initialization steps for DCAN. Figure 3-2, Figure 3-3, and Figure 3-4 show the initialization steps for MCAN.

# 3.4 Code Snippets for Module Initialization

Code snippets for module initialization is shown in the following figures.

```

1 main()

2 {

3

11

// Initialize device clock and peripherals

4

5

11

6

Device_init();

7

8

11

// Initialize GPIO and configure GPIO pins for CANTX/CANRX

9

10

11

11

Device_initGPIO();

12

13

11

14

// Configuring the GPIOs for DCAN.

15

11

GPI0_setPinConfig(DEVICE_GPI0_CFG_CANRXA);

16

17

GPIO setPinConfig(DEVICE GPIO CFG CANTXA);

18

19

11

// Initialize the CAN controller

20

21

11

22

CAN_initModule(CANA_BASE);

23

24

11

25

// Set up the CAN bus bit rate to 500 kbps

26

11

27

CAN setBitRate(CANA BASE, DEVICE SYSCLK FREQ, 500000, 16);

28

29

11

// Initialize the transmit message object used for sending CAN messages.

30

31

11

32

CAN setupMessageObject(CANA BASE, TX MSG OBJ ID, 0x1,

33

CAN MSG FRAME STD, CAN MSG OBJ TYPE TX, 0,

34

CAN MSG OBJ NO FLAGS, MSG DATA LENGTH);

35

36

11

37

// Initialize the receive message object used for receiving CAN messages.

38

11

39

CAN setupMessageObject(CANA BASE, RX MSG OBJ ID, 0x1,

40

CAN MSG FRAME STD, CAN MSG OBJ TYPE RX, 0,

41

CAN_MSG_OBJ_NO_FLAGS, MSG_DATA_LENGTH);

42

43

11

44

// Start CAN module operations

45

11

46

CAN_startModule(CANA_BASE);

47 }

```

Figure 3-1. DCAN Initialization

```

1//

2 // Function Prototype.

3//

4 static void MCANConfig(void);

5

6 main()

7 {

8

11

9

// Initialize device clock and peripherals

10

11

Device_init();

11

12

13

11

// Initialize GPIO and unlock the GPIO configuration registers

14

15

11

16

Device initGPIO();

17

18

11

19

// Configuring the GPIOs for MCAN.

11

20

21

GPIO setPinConfig(DEVICE GPIO CFG MCANRXA);

GPI0_setPinConfig(DEVICE_GPI0_CFG_MCANTXA);

22

23

#ifdef F2838x

24

25

11

// Allocate shared peripheral to C28x (Applicable only for 320F2838x)

26

27

11

SysCtl allocateSharedPeripheral(SYSCTL PALLOCATE MCAN A,0x0U);

28

29

30

11

// Configure the divisor for the MCAN bit-clock

31

32

11

SysCtl_setMCANClk(SYSCTL_MCANCLK_DIV_5);

33

#else

34

35

11

// Configure the divisor for the MCAN bit-clock

36

37

11

38

SysCtl_setMCANClk(SYSCTL_MCANCLK_DIV_3);

39

#endif

40

41

11

42

// Configure MCAN (shown separately)

43

11

44

MCANConfig();

45 }

```

Figure 3-2. MCAN GPIO and Clock Initialization

Module Initialization

```

50 static void MCANConfig(void)

51 {

52

MCAN_InitParams initParams;

53

MCAN ConfigParams configParams;

54

MCAN MsgRAMConfigParams msgRAMConfigParams;

55

MCAN MsgRAMConfigParams

msgRAMConfigParams;

56

MCAN BitTimingParams

bitTimes;

57

58

11

59

// Initializing all structs to zero to prevent stray values

60

11

memset(&initParams, 0, sizeof(initParams));

61

62

memset(&configParams, 0, sizeof(configParams));

63

memset(&msgRAMConfigParams, 0, sizeof(msgRAMConfigParams));

64

memset(&bitTimes, 0, sizeof(bitTimes));

65

66

11

67

// Initialize MCAN Init parameters.

68

11

initParams.fdMode

= 0x0U; // FD operation disabled.

69

70

initParams.brsEnable

= 0x0U; // Bit rate switching for

71

// transmissions disabled.

= 0x0U; // Transmit pause disabled.

72

initParams.txpEnable

73

initParams.darEnable

= 0x1U; // Disable Automatic retransmission of

74

// messages not transmitted successfully

initParams.tdcEnable

= 0x1U; // Transmitter Delay Compensation is

75

76

// enabled.

initParams.wdcPreload

77

= 0xFFU;// Start value of the Message RAM

78

// Watchdog Counter preload.

79

80

11

// Initialize MCAN Config parameters.

81

82

11

= 0x0U; // Normal CAN operation.

83

configParams.asmEnable

configParams.tsPrescalar

= 0xFU; // Prescaler Value.

84

= 0x0U; // Timestamp counter value.

85

configParams.tsSelect

86

configParams.timeoutSelect

= MCAN TIMEOUT SELECT CONT;

// Time-out counter source select.

87

88

configParams.timeoutPreload

= 0xFFFFU; // Start value of the Timeout

89

// Counter.

configParams.timeoutCntEnable = 0x0U; // Time-out Counter is disabled.

90

configParams.filterConfig.rrfs = 0x1U; // Reject all remote frames with

91

92

// 29-bit extended IDs.

configParams.filterConfig.rrfe = 0x1U; // Reject all remote frames with

93

94

// 11-bit standard IDs.

95

configParams.filterConfig.anfe = 0x2U; // Reject Non-Matching Frames Extended

96

configParams.filterConfig.anfs = 0x2U; // Reject Non-Matching Frames Standard

97

//**********

98

99

// Message RAM Configuration Section Here

//***********

100

101

//*********

102

103

// Bit Timing Configuration Section Here

104

//****

```

## Figure 3-3. MCAN Operating Mode and Global Filter Configuration

```

107

11

// Wait for Memory initialization to be completed.

108

109

11

110

while(FALSE == MCAN_isMemInitDone(MCANA_DRIVER_BASE));

111

112

11

113

// Put MCAN in SW initialization mode.

114

11

115

MCAN setOpMode(MCANA DRIVER BASE, MCAN OPERATION MODE_SW INIT);

116

117

11

// Wait till MCAN is not initialized.

118

119

11

120

while (MCAN OPERATION MODE SW INIT != MCAN getOpMode(MCANA DRIVER BASE));

121

122

11

123

// Initialize MCAN module.

124

11

125

MCAN init(MCANA DRIVER BASE, &initParams);

126

127

11

128

// Configure MCAN module.

129

11

130

MCAN config(MCANA DRIVER BASE, &configParams);

131

132

11

133

// Configure Bit timings.

134

11

135

MCAN setBitTime(MCANA DRIVER BASE, &bitTimes);

136

137

11

138

// Configure Message RAM Sections

139

11

140

MCAN_msgRAMConfig(MCANA_DRIVER_BASE, &msgRAMConfigParams);

141

142

11

143

// Take MCAN out of the SW initialization mode

144

11

145

MCAN setOpMode(MCANA DRIVER BASE, MCAN OPERATION MODE NORMAL);

146

while (MCAN OPERATION MODE NORMAL != MCAN getOpMode(MCANA DRIVER BASE));

147

```

### Figure 3-4. MCAN Initialization completion

# **4 Bit Timing Configuration**

Bit timing configuration differs between classic CAN and CAN FD. The process is *relatively* easier in classic CAN, since the bit-rate is the same for the entire frame. However, in CAN FD, two different bit-rates can be used: a slower "nominal" bit-rate and a faster "data" bit-rate. In the MCAN module, these two bit-rates are configured by writing to the *MCAN\_NBTP* and *MCAN\_DBTP* registers respectively during the module initialization. Note that an application can choose to only take advantage of the higher number of data bytes per frame that can be transmitted in CAN FD and use the same bit-rate for the entire frame. The faster bit-rate for the data phase also warrants Transmitter Delay Compensation (TDC) without which bit errors can occur. Below is an example for calculating bit-timing parameters:

### Example 1

Assume the following parameters are desired with a CAN module clock of 200 MHz:

Nominal bit-rate = 500kbps, Data bit-rate = 2Mbps.

$$Bit - rate = \frac{CAN \text{ module clock}}{Bit - rate \text{ prescaler } \times Bit - time}$$

TEXAS INSTRUMENTS www.ti.com

(1)

For a nominal bit-rate of 500kbps, the product of *Bit-rate prescaler x Bit-time* must be equal to 400. This can be achieved with multiple combinations of the prescaler and bit-time, as long as the rules laid out by the CAN protocol are not violated. For example, a prescaler of 20 and a bit-time of 20 TQ can be chosen. A prescaler of 20 (NBRP<sub>reg</sub> = 19) yields a bit-clock of 10 MHz with a resultant time-quanta (TQ) of 100 ns. A bit-time of 20 TQ can be achieved with multiple combinations for TSEG1 and TSEG2 resulting in varying sample-points (SP).

Bit-time =  $(NTSEG1_{reg} + 1) + (NTSEG2_{reg} + 1) + 1$ , where  $NTSEG1_{reg}$  and  $NTSEG2_{reg}$  represent the actual values written into *MCAN\_NBTP.NTSEG1* and *MCAN\_NBTP.NTSEG2* bit-fields respectively. If TSEG1 is chosen to be 16 ( $NTSEG1_{reg} = 15$ ) and TSEG2 is chosen to be 4 ( $NTSEG2_{reg} = 3$ ), those values yield a sampling-point of 80%. By adjusting the TSEG1 and TSEG2 values, the sampling-point can be moved within the bit-time based on the network parameters.

Similar calculation is used for data bit-rate of 2Mbps. For a data bit-rate of 2Mbps, the product of *Bit-rate prescaler x Bit-time* must be equal to 100. This can be achieved with multiple combinations of the prescaler and bit-time, as long as the rules laid out by the CAN protocol are not violated. For example, a prescaler of 5 and a bit-time of 20 TQ can be chosen. A prescaler of 5 (DBRP<sub>reg</sub> = 4) yields a bit-clock of 40 MHz with a resultant time-quanta (TQ) of 25ns. A bit-time of 20 TQ can be achieved with multiple combinations for TSEG1 and TSEG2 resulting in varying sample-points (SP).

Bit-time =  $(DTSEG1_{reg} + 1) + (DTSEG2_{reg} + 1) + 1$ , where  $DTSEG1_{reg}$  and  $DTSEG1_{reg}$  represent the actual values written into *MCAN\_DBTP.DTSEG1* and *MCAN\_DBTP.DTSEG2* bit-fields respectively. If TSEG1 is chosen to be 16 ( $DTSEG1_{reg} = 15$ ) and TSEG2 is chosen to be 4 ( $NTSEG2_{reg} = 3$ ), those values yield a sampling-point of 80%. By adjusting the TSEG1 and TSEG2 values, the sampling-point can be moved within the bit-time based on the network parameters.

```

1

11

// Initialize bit timings.

2

3

11

4

bitTimes.nomRatePrescalar = 0xBU; // Nominal Baud Rate Pre-scaler

bitTimes.nomTimeSeg1 = 0x2U; // Nominal Time segment before SP

5

bitTimes.nomTimeSeg2

= 0x0U; // Nominal Time segment after SP

6

7

bitTimes.nomSynchJumpWidth = 0x0U; // Nominal SJW

bitTimes.dataRatePrescalar = 0x1U; // Data Baud Rate Pre-scaler

8

9

bitTimes.dataTimeSeg1

= 0xAU; // Data Time segment before SP

10

bitTimes.dataTimeSeg2

= 0x2U; // Data Time segment after SP

bitTimes.dataSynchJumpWidth = 0x2U; // Data SJW

11

12

// The above is just an illustrative example. You must compute the timing values

13

14

// based on your network paramters such as oscillator accuracy, propagation delay

// introduced by the transceivers and the bus.

15

16

```

## Figure 4-1. MCAN Bit-timing Configuration

# **5 Message RAM Configuration**

In DCAN, Message RAM can only be accessed by the Message Handler. The *Driverlib* APIs interact with the Message Interface (IFx) registers which carry out the read or write operations with the Message RAM. In MCAN, *Driverlib* APIs can be used to carry out the read or write operations with the Message RAM directly.

The Message RAM is structured differently in MCAN as compared to DCAN. In DCAN, the number of message objects in the Message RAM is fixed at 32 and each message object can be configured for either transmit or receive operation.

However, in MCAN, Message RAM can be configured to have the following sections:

- Standard Filter Element

- Extended Filter Element

- Rx Buffer

- Rx FIFO

- Tx Buffer

- Tx FIFO or Tx Queue

- Tx Event FIFO

The design of MCAN Message RAM offers tremendous flexibility, enabling allocation of the available memory to each of the sections mentioned above based on the application needs. The sections can be ordered in any manner and the unused sections can be allocated zero memory. Note that Message RAM size can vary from one device to another. Refer the device-specific data sheet for more information.

Message RAM configuration involves defining the following:

- Starting address for every section used.

- The number of elements in each section.

- The size of the elements which is different for different size of data packets as can be seen in Table 5-1 (Filter Elements and Tx Event FIFO have fixed sizes).

These values are written to specific registers and are subsequently used by both the Message Handler and *Driverlib* APIs to interact with the Message RAM. Hence, Message RAM configuration is a crucial step for MCAN during module initialization, while such configuration is not required in DCAN. The MCAN module addresses the Message RAM in 32-bit words. Consequently, all sections are of sizes that are multiples of 32-bit words.

| MCAN_RXESC.RBDS/<br>MCAN_RXESC.F0DS/<br>MCAN_RXESC.F1DS/<br>MCAN_TXESC.TBDS<br>(Corresponding to Rx Buffer, Rx FIFOs<br>and Tx Buffer, respectively) | Data Field (bytes) | FIFO Element Size (or) Buffer Element<br>Size [RAM words] |

|------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------|-----------------------------------------------------------|

| 000                                                                                                                                                  | 8                  | 4                                                         |

| 001                                                                                                                                                  | 12                 | 5                                                         |

| 010                                                                                                                                                  | 16                 | 6                                                         |

| 011                                                                                                                                                  | 20                 | 7                                                         |

| 100                                                                                                                                                  | 24                 | 8                                                         |

| 101                                                                                                                                                  | 32                 | 10                                                        |

| 110                                                                                                                                                  | 48                 | 14                                                        |

| 111                                                                                                                                                  | 64                 | 18                                                        |

### Table 5-1. Element Size Vs Size of Data Packets

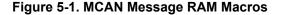

Macros are available in *C2000ware* examples which automatically calculate the starting address for each section when the number and size of elements are set by the user. This configuration can be successfully utilized in any application. Multiple valid configurations are possible and there is not a single "correct" configuration. Note that the MCAN module does not check for invalid configurations. It is the responsibility of the user to verify that sections do not overlap each other or exceed the available RAM.

#### Message RAM Configuration

27 #define MCAN\_TX\_EVENT\_START\_ADDR

29

1// 2// Defines 3// 3// 4 #define MCAN\_STD\_ID\_FILTER\_NUM 5 #define MCAN\_EXT\_ID\_FILTER\_NUM 6 #define MCAN\_FIFO\_0\_FLEM\_SIZE 8 #define MCAN\_FIFO\_1\_NUM 9 #define MCAN\_FIFO\_1\_LEM\_SIZE 10 #define MCAN\_RX\_BUFF\_LEM\_SIZE 12 #define MCAN\_TX\_BUFF\_SIZE 13 #define MCAN\_TX\_BUFF\_SIZE 13 #define MCAN\_TX\_BUFF\_SIZE (1U) (0U) (5U) (MCAN\_ELEM\_SIZE\_64BYTES) (10U) (MCAN\_ELEM\_SIZE\_64BYTES) (10U) (MCAN\_ELEM\_SIZE\_64BYTES) (10U) 13 #define MCAN\_TX\_FQ\_SIZE 14 #define MCAN\_TX\_BUFF\_ELEM\_SIZE (0U) (MCAN\_ELEM\_SIZE\_64BYTES) 15 #define MCAN\_TX\_EVENT\_SIZE (100) 16 17 // 17// Defining Starting Addresses for Message RAM Sections, 18// (Calculated from Macros based on User defined configuration above) 20// 21 #define MCAN\_STD\_ID\_FILT\_START\_ADDR 22 #define MCAN\_EXT\_ID\_FILT\_START\_ADDR (0x0U) 23 #define MCAN\_FIF0\_0\_START\_ADDR 24 #define MCAN\_FIF0\_0\_START\_ADDR 25 #define MCAN\_RX\_BUFF\_START\_ADDR 26 #define MCAN\_TX\_BUFF\_START\_ADDR

(0x0U) (MCAN\_STD\_ID\_FILT\_START\_ADDR + ((MCAN\_STD\_ID\_FILTER\_NUM \* MCANSS\_STD\_ID\_FILTER\_SIZE\_WORDS \* 4U))) (MCAN\_EXT\_ID\_FILT\_START\_ADDR + ((MCAN\_EXT\_ID\_FILTER\_INUM \* MCANSS\_STT\_ID\_FILTER\_SIZE\_WORDS \* 4U))) (MCAN\_FIF0\_0\_START\_ADDR + (MCAN\_getMsg0bjSize(MCAN\_FIF0\_0\_ELEM\_SIZE) \* 4U \* MCAN\_FIF0\_0\_NUM)) (MCAN\_FIF0\_1\_START\_ADDR + (MCAN\_getMsg0bjSize(MCAN\_FIF0\_1\_ELEM\_SIZE) \* 4U \* MCAN\_FIF0\_1\_NUM)) (MCAN\_FIF0\_START\_ADDR + (MCAN\_getMsg0bjSize(MCAN\_RX\_BUFF\_ELEM\_SIZE) \* 4U \* MCAN\_RX\_BUFF\_NUM)) (MCAN\_TX\_BUFF\_START\_ADDR + (MCAN\_getMsg0bjSize(MCAN\_TX\_BUFF\_ELEM\_SIZE) \* 4U \* MCAN\_RX\_BUFF\_SIZE + MCAN\_TX\_FQ\_SIZE)))

| 29 |                                                                         |                                       |  |

|----|-------------------------------------------------------------------------|---------------------------------------|--|

| 30 | 11                                                                      |                                       |  |

| 31 | <pre>// Initialize Message RAM Sections Conf</pre>                      | figuration Parameters.                |  |

| 32 | //                                                                      |                                       |  |

| 33 | msgRAMConfigParams.flssa                                                | = MCAN STD ID FILT START ADDR;        |  |

| 34 | // Standard ID Filter List Start Addres                                 | ss.                                   |  |

| 35 | msgRAMConfigParams.lss                                                  | <pre>= MCAN_STD_ID_FILTER_NUM;</pre>  |  |

| 36 | // List Size: Standard ID.                                              | /                                     |  |

| 37 | msgRAMConfigParams.flesa                                                | = MCAN EXT ID FILT START ADDR;        |  |

| 38 | // Extended ID Filter List Start Addres                                 |                                       |  |

| 39 | msgRAMConfigParams.lse                                                  | = MCAN_EXT_ID_FILTER_NUM;             |  |

| 40 | // List Size: Extended ID.                                              |                                       |  |

| 41 | msgRAMConfigParams.txStartAddr                                          | = MCAN TX BUFF START ADDR;            |  |

| 42 | // Tx Buffers Start Address.                                            | ······,                               |  |

| 43 | msgRAMConfigParams.txBufNum                                             | = MCAN TX BUFF SIZE;                  |  |

| 44 | <pre>// Number of Dedicated Transmit Buffers</pre>                      |                                       |  |

| 45 | msgRAMConfigParams.txFIFOSize                                           | = MCAN TX FQ SIZE;                    |  |

| 46 | // Number of Tx FIFO or Tx Queue Elemen                                 |                                       |  |

| 47 | msgRAMConfigParams.txBufMode                                            | = OU; //Tx FIFO operation             |  |

| 48 | msgRAMConfigParams.txBufElemSize                                        | = MCAN TX BUFF ELEM SIZE;             |  |

| 49 | // Tx Buffer Element Size.                                              | - head_fx_boin_ceen_512e,             |  |

| 50 | msgRAMConfigParams.txEventFIFOStartAddr                                 | - MCAN TX EVENT START ADDR.           |  |

| 51 | // Tx Event FIFO Start Address.                                         | - (CAN_IX_EVENT_51AKT_ADDR)           |  |

| 52 | msgRAMConfigParams.txEventFIF0Size                                      | = MCAN TX BUFF SIZE;                  |  |

| 53 | // Event FIFO Size.                                                     | - HCAN_TX_BOTT_512E,                  |  |

| 54 | msgRAMConfigParams.txEventFIFOWaterMark                                 | < - 311.                              |  |

| 55 | // Level for Tx Event FIFO watermark in                                 |                                       |  |

| 56 | msgRAMConfigParams.rxFIF00startAddr                                     |                                       |  |

| 57 | // Rx FIF00 Start Address.                                              | = MCAN_FIFU_0_START_ADDR;             |  |

| 58 | msgRAMConfigParams.rxFIF00size                                          | = MCAN FIFO 0 NUM;                    |  |

| 59 | // Number of Rx FIFO elements.                                          | = MCAN_PIPO_0_NON;                    |  |

| 60 | msgRAMConfigParams.rxFIF00waterMark                                     | = 3U; // Rx FIFO0 Watermark.          |  |

| 61 | msgRAMConfigParams.rxFIF000pMode                                        | = 0U; // FIFO blocking mode.          |  |

| 62 | msgRAMConfigParams.rxFIF01startAddr                                     | = MCAN FIFO 1 START ADDR;             |  |

| 63 | // Rx FIF01 Start Address.                                              | = MCAN_FIFO_1_START_ADDR;             |  |

| 64 | msgRAMConfigParams.rxFIF01size                                          | - MCAN ETEO 1 NUM                     |  |

| 65 | // Number of Rx FIFO elements.                                          | <pre>= MCAN_FIF0_1_NUM;</pre>         |  |

| 66 | msgRAMConfigParams.rxFIF01waterMark                                     | = 3U; // Level for Rx FIFO 1          |  |

| 67 | msgRAmconfigParams.rxfif01watermark                                     | // watermark interrupt.               |  |

| 68 | non Bawan fin Branne av ETEO10-Mada                                     | = OU; // FIFO blocking mode.          |  |

| 69 | msgRAMConfigParams.rxFIF010pMode                                        |                                       |  |

| 70 | msgRAMConfigParams.rxBufStartAddr<br>// Rx Buffer Start Address.        | <pre>= MCAN_RX_BUFF_START_ADDR;</pre> |  |

| 70 | msgRAMConfigParams.rxBufElemSize                                        | MCAN BY BUCK FLEW CTTE.               |  |

|    |                                                                         | <pre>= MCAN_RX_BUFF_ELEM_SIZE;</pre>  |  |

| 72 | // Rx Buffer Element Size.                                              | - MCAN ETEO O ELEM STZE               |  |

| 73 | msgRAMConfigParams.rxFIF00ElemSize                                      | = MCAN_FIFO_0_ELEM_SIZE;              |  |

| 74 | // Rx FIFO0 Element Size.                                               | MCAN FIED A FLEW STREET               |  |

| 75 | <pre>msgRAMConfigParams.rxFIF01ElemSize // Rx FIF01 Element Size.</pre> | <pre>= MCAN_FIF0_1_ELEM_SIZE;</pre>   |  |

| 76 | // KX FIPUI Element Size.                                               |                                       |  |

|    |                                                                         |                                       |  |

#### Figure 5-2. MCAN Message RAM Initialization

# 6 Interrupt handling

From a CPU level (PIE, IFR and INTM), interrupt handling is identical between DCAN and MCAN. However, interrupt handling differs significantly at the module level. Table 6-1 summarizes the basic differences in interrupt handling between DCAN and MCAN modules:

| Category                                     | DCAN                                                                                                                | MCAN                                                                                                                                                                                                                                                                                             |

|----------------------------------------------|---------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Interrupt sources                            | Error, Status and Transmission/Reception<br>interrupts corresponding to each message<br>object                      | 30 internal interrupt sources (specified in table below )                                                                                                                                                                                                                                        |

| Global interrupt registers                   | Registers to enable, read and clear global interrupts present                                                       | Corresponding register is absent                                                                                                                                                                                                                                                                 |

| Configuring reception interrupt              | Reception interrupt can be separately<br>enabled by setting RxIE bit in each Message<br>Object as required          | Interrupt can be enabled or disabled for any<br>new message being received in dedicated Rx<br>Buffer.                                                                                                                                                                                            |

| Determining source of receive interrupt      | Value read from register CAN_INT<br>corresponds to Message Object Number<br>where message has been received in      | Interrupt only denotes that a new message<br>has been received in Rx Buffer. Value read<br>from MCAN_NDATx registers corresponds to<br>Rx Buffer element number where message<br>has been received.                                                                                              |

| Rx FIFO interrupts                           | No separate interrupt functionality supported                                                                       | Additional interrupt sources available<br>including New Message in FIFO, FIFO<br>being full and FIFO Watermark Reached<br>(Watermark can be configured during<br>Message RAM configuration to generate an<br>interrupt when FIFO is filled to a certain level<br>to serve the application needs) |

| Configuring transmission interrupts          | Transmission interrupt can be separately<br>enabled by setting TxIE bit in each Message<br>Object as required       | Transmission interrupt can be separately<br>enabled by configuring the register<br>MCAN_TXBTIE, where each bit corresponds<br>to a separate Tx Buffer Element.                                                                                                                                   |

| Determining Source of transmission interrupt | Value read from register CAN_INT<br>corresponds to Message Object Number<br>where message has been transmitted from | Interrupt only denotes that a transmission<br>has been completed. Value read from the<br>MCAN_TXBTO register corresponds to the<br>Tx Buffer element number from which the<br>transmission has occurred.                                                                                         |

## 6.1 MCAN Interrupt Sources

The different interrupt sources for MCAN have been documented in Table 6-2:

| Table 6-2. MCAN Interrupt Sources |                                     |  |

|-----------------------------------|-------------------------------------|--|

| Interrupt                         | Description                         |  |

| ARA                               | Access to Reserved Address          |  |

| PED                               | Protocol Error in Data Phase        |  |

| PEA                               | Protocol Error in Arbitration Phase |  |

| WDI                               | Watchdog                            |  |

| во                                | Bus-off                             |  |

| EW                                | Warning Status                      |  |

| EP                                | Error Passive                       |  |

| ELO                               | Error Logging Overflow              |  |

| BEU                               | Bit Error Uncorrected               |  |

### Table 6-2. MCAN Interrupt Sources

| Table 6-2. MCAN Interrupt Sources (continued) |                                       |  |

|-----------------------------------------------|---------------------------------------|--|

| Interrupt                                     | Description                           |  |

| BEC                                           | Bit Error Corrected                   |  |

| DRX                                           | Message Stored to Dedicated Rx Buffer |  |

| ТОО                                           | Timeout Occurred                      |  |

| MRAF                                          | Message RAM Access Failure            |  |

| TSW                                           | Timestamp Wraparound                  |  |

| TEFL                                          | Tx Event FIFO Element Lost            |  |

| TEFF                                          | Tx Event FIFO Full                    |  |

| TEFW                                          | Tx Event FIFO Watermark Reached       |  |

| TEFN                                          | Tx Event FIFO New Entry               |  |

| TFE                                           | Tx FIFO Empty                         |  |

| TCF                                           | Transmission Cancellation Finished    |  |

| TC                                            | Transmission Completed                |  |

| НРМ                                           | High Priority Message                 |  |

| RF1L                                          | Rx FIFO 1 Message Lost                |  |

| RF1F                                          | Rx FIFO 1 Full                        |  |

| RF1W                                          | Rx FIFO 1 Watermark Reached           |  |

| RF1N                                          | Rx FIFO 1 New Message                 |  |

| RF0L                                          | Rx FIFO 0 Message Lost                |  |

| RF0F                                          | Rx FIFO 0 Full                        |  |

| RF0W                                          | Rx FIFO 0 Watermark Reached           |  |

| RF0N                                          | Rx FIFO 0 New Message                 |  |

## 6.2 DCAN Interrupt Handling

## **Device-level Interrupt Configurations:**

1. Initialize PIE and PIE Vector Table. Enable Global and Real-time Interrupts.

T-LL OO MOANLESS

2. Configure the interrupt handler in the PIE Vector Table. Enable interrupt in the interrupt controller.

## Module-level Interrupt Configurations

- 1. Enable Error and Status interrupts, using the CAN Control Register (CAN\_CTL). Enable Message Object interrupts while setting up Message Objects individually.

- 2. Select interrupt line where each message object interrupt is to be routed using the register (CAN\_IP\_MUX21), where each bit corresponds to a single message object.

- 3. Interrupt Service Routine (ISR) : Read Interrupt Register (CAN\_INT) to determine the source of the interrupt (status/error/particular message object). Clear the Interrupt by writing to CAN Error and Status Register (CAN\_ES) or by clearing the *IntPnd* bit in the corresponding Message Object. Clear the Global Interrupt Flag for the corresponding Interrupt Line.

- 4. Acknowledge the interrupt via PIEACK.

TEXAS INSTRUMENTS www.ti.com

```

1//

2 // Function Prototypes

3//

4 interrupt void canISR(void);

5

6 {

7

11

// Initialize PIE and clear PIE registers. Disables CPU interrupts.

8

9

11

10

Interrupt_initModule();

11

12

11

13

// Initialize the PIE vector table with pointers to the shell Interrupt

// Service Routines (ISR).

14

15

11

16

Interrupt_initVectorTable();

17

// Enable Global Interrupt (INTM) and realtime interrupt (DBGM)

18

19

11

20

EINT;

ERTM;

21

22

// Interrupts that are used in this example are re-mapped to

23

24

// ISR functions found within this file.

25

// This registers the interrupt handler in PIE vector table.

26

11

Interrupt_register(INT_CANA0,&canaISR);

27

28

29

11

30

// Enable the CAN-A interrupt signal

31

11

32

Interrupt enable(INT CANA0);

33

34

11

// Enable interrupts on the CAN A peripheral. (error, status, line 0/1)

35

36

11

CAN enableInterrupt(CANA BASE, CAN INT IE0 | CAN INT ERROR |

37

CAN INT STATUS);

38

39

40

// Enable Global Interrupt for corresponding interrupt line

41

42

CAN enableGlobalInterrupt(CANA BASE, CAN GLOBAL INT CANINT0);

43

44

11

// Transmit/Receive Interrupt enabled during setup Message object Function

45

46

11

47

CAN setupMessageObject(CANA BASE, TX MSG OBJ ID, 0x15555555,

CAN MSG FRAME EXT, CAN MSG_OBJ_TYPE_TX, 0,

48

49

CAN MSG OBJ TX INT ENABLE, MSG DATA LENGTH);

50

51

// Select Interrupt Line for each mailbox

52

11

53

CAN_setInterruptMux(CANA_BASE, mux);

54

55 }

```

#### Figure 6-1. DCAN Interrupt Initialization

Interrupt handling

```

57 //

58 // CAN A ISR - The interrupt service routine called when a CAN interrupt is

59 //

triggered on CAN module A.

60//

61 __interrupt void

62 canaISR(void)

63 {

64

uint32_t status;

65

// Read the CAN-A interrupt status to find the cause of the interrupt

66

67

68

status = CAN getInterruptCause(CANA BASE);

69

// If the cause is a controller status interrupt, then get the status

70

71

72

if(status == CAN INT INT0ID STATUS)

// Read the controller status.

73

{

74

status = CAN getStatus(CANA BASE);

75

76

// Check to see if an error occurred.

77

78

if(((status & ~(CAN STATUS TXOK)) != CAN STATUS LEC MSK) &&

79

((status & ~(CAN STATUS TXOK)) != CAN STATUS LEC NONE))

80

{

81

errorFlag = 1;

// Set a flag to indicate some errors may have occurred.

82

}

83

3

else if(status == TX_MSG_OBJ_ID)

84

85

{

86

// Transmit Message handling will go here

87

CAN_clearInterruptStatus(CANA_BASE, TX_MSG_OBJ_ID); // Clear the message object interrupt

88

89

}

90

else if(status == RX MSG OBJ ID)

91

{

// Receive message handling will go here

92

93

94

CAN_clearInterruptStatus(CANA_BASE, RX_MSG_OBJ_ID); // Clear the message object interrupt

95

}

96

97

else

98

{

99

11

100

// Spurious interrupt handling can go here.

101

11

102

}

103

104

11

// Clear the global interrupt flag for the CAN interrupt line

105

106

11

CAN_clearGlobalInterruptStatus(CANA_BASE, CAN_GLOBAL_INT_CANINT0);

107

108

109

11

110

// Acknowledge this interrupt located in group 9

111

11

Interrupt clearACKGroup(INTERRUPT ACK GROUP9);

112

113 }

```

## Figure 6-2. DCAN Interrupt handling

## 6.3 MCAN Interrupt Handling

### **Device-level Interrupt Configurations:**

- 1. Initialize PIE and PIE Vector Table. Enable Global and Real-time Interrupts.

- 2. Configure the interrupt handler in the PIE Vector Table. Enable interrupt in the interrupt controller.

### **Module-level Interrupt Configurations**

- 1. Enable interrupt sources using the register (MCAN\_IR), where each bit corresponds to a single interrupt source. Enable interrupt lines as required using the register (MCAN\_ILE).

- 2. Select interrupt lines where interrupt source is to be routed using the register (MCAN\_ILS), where each bit corresponds to a single interrupt source.

- 3. Interrupt Service Routine (ISR) : Read Interrupt Register (MCAN\_IR) to determine the source of the interrupt (any of the 30 individual interrupt sources). Clear the interrupt by writing to the same register. Clear the interrupt line by writing to the register (MCANSS\_EOI).

- 4. Acknowledge the interrupt via PIEACK.

```

1

2//

3 // Function Prototype.

411

5 static void MCANIntrConfig(void);

6 __interrupt void MCANIntr1ISR(void);

8 {

9

11

// ISR Configuration.

10

11

11

12

MCANIntrConfig();

13

14

// Enable Interrupts.

15

// (interrupts can be enabled individually by modifying the second parameter)

16

11

17

MCAN_enableIntr(MCANA_DRIVER_BASE, MCAN_INTR_MASK_ALL, 10);

18

19

11

20

// Select Interrupt Line.

21

// (interrupt line can be individually chosen for each interrupt source)

11

22

23

MCAN_selectIntrLine(MCANA_DRIVER_BASE, MCAN_INTR_MASK_ALL, MCAN_INTR_LINE_NUM_1);

24

25

11

26

// Enable Interrupt Line.

27

11

28

MCAN enableIntrLine(MCANA DRIVER BASE, MCAN INTR LINE NUM 1, 1U);

29

30

11

31

// Enable Transmission interrupt.

// (Needs to be done individually for each Tx Buffer Element)

32

33

// (Additionally, transmission related interrupt sources will need to be enabled above,

34

// as desired by application)

35

MCAN_txBufTransIntrEnable(MCANA_DRIVER_BASE, 1U, 1U);

36 }

37

38 / /

39 // This function will configure X-BAR for MCAN interrupts.

40 / /

41 static void MCANIntrConfig(void)

42 {

43

44

Interrupt_initModule();

45

Interrupt_initVectorTable();

46

47

Interrupt_register(INT_MCANA_1,&MCANIntr1ISR);

48

Interrupt_enable(INT_MCANA_1);

49

50

Interrupt_enableGlobal();

51 }

```

### Figure 6-3. MCAN Interrupt Initialization

### TEXAS INSTRUMENTS www.ti.com

#### Interrupt handling

53 // 54 // This is Interrupt Service Routine for MCAN interrupt 1. 55 // 56 interrupt void MCANIntr1ISR(void) 57 { 58 uint32\_t intrStatus; 59 intrStatus = MCAN getIntrStatus(MCANA DRIVER BASE); 60 61 // Clearing the corresponding interrupt line 62 63 HW\_WR\_FIELD32(MCANA\_DRIVER\_BASE + MCAN\_MCANSS\_EOI, MCAN\_MCANSS\_EOI, 0x2); 64 65 66 // Clear the interrupt Status. 67 11 68 MCAN clearIntrStatus(MCANA DRIVER BASE, intrStatus); 69 70 71 // Check to see if the interrupt is caused by 11 72 reception of new message in dedicated Rx Buffer 73 11 if((MCAN\_INTR\_SRC\_DEDICATED\_RX\_BUFF\_MSG & intrStatus) == MCAN\_INTR\_SRC\_DEDICATED\_RX\_BUFF\_MSG) 74 75 { 76 1 // Receive Message Handling will go here 77 78 } 11 79 80 Check to see if the interrupt is caused by 11 81 reception of new message in Rx FIFO 1 11 82 11 if((MCAN\_INTR\_SRC\_RX\_FIF01\_NEW\_MSG & intrStatus) == MCAN\_INTR\_SRC\_RX\_FIF01\_NEW\_MSG) 83 84 { 85 // Receive Message Handling will go here 86 87 } 88 11 Check to see if the interrupt is caused by 89 11 completion of transmission of message 90 11 91 11 92 if((MCAN\_INTR\_SRC\_TRANS\_COMPLETE & intrStatus) == MCAN\_INTR\_SRC\_TRANS\_COMPLETE) 93 { 94 // Transmit Message Handling will go here 95 96 } 97 11 // Similar logic can be implemented to check for other interrupt sources and determine 98 99 // the actions based on the needs of the application 100 11 101 102 // Acknowledge this interrupt located in group 9 103 11 104 Interrupt\_clearACKGroup(INTERRUPT\_ACK\_GROUP9); 105 }

Figure 6-4. MCAN Interrupt Handling

# 7 Transmitting data

The overall transmission process is largely identical between DCAN and MCAN modules. The differences stem primarily from how the Message RAM is laid out and utilized. Also, MCAN frames can be longer and employ two different bit-rates. Once configured appropriately, the module takes care of bit-rate switching and handling the larger payload. No code intervention is needed at that point.

### 7.1 Basic Transmission Process

This section outlines the flow including the actions required and the registers involved in the process of transmitting a frame using DCAN and MCAN.

### 7.1.1 Transmission with DCAN

- 1. Setup a transmit Message Object.

- 2. Write to the IFx registers which in turn writes the Message ID (ARBID), DLC and data to the Message Object (and update Message ID, if warranted).

- 3. Set TXRQST bit in the IFx register (CAN\_IFxCMD) to signal that Message Object is ready for transmission.

- 4. When bus is idle, Message Handler parses Message Objects ready for transmission and transmits the highest priority Message available.

### 7.1.2 Transmission with MCAN

- 1. Initialize Transmit Buffer Element (defined as a structure).

- 2. Write Tx Message to Message RAM.

- 3. Set the bit corresponding to the Tx Buffer Element Number in the *MCAN\_TXBAR* register (each bit represents a separate buffer element) to signal that message is ready for transmission.

- 4. When bus is idle, Message Handler parses Buffer Elements ready for transmission and transmits the highest priority Message available.

## 7.2 MCAN Vs DCAN Transmit Procedural Differences

Although the conceptual procedure for transmission is largely identical for DCAN and MCAN, Table 7-1 captures the key differences between both modules:

| Category                          | DCAN                                                                                    | MCAN                                                                                                            |

|-----------------------------------|-----------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------|

| Transmit Priority                 | Numerically lowest Message Object (that is ready for transmission) is transmitted first | Buffer containing numerically lowest<br>Message ID (among those ready for<br>transmission) is transmitted first |

| Buffer Type                       | Only Transmit Message Object                                                            | Transmit Buffers can be configured as<br>Dedicated Tx Buffers, Tx FIFO or Tx Queue                              |

| Writing/Updating Transmit Message | Requires Writes to IFx registers                                                        | Transmit Message can be updated by writing directly to Message RAM using <i>Driverlib</i> APIs                  |

### Table 7-1. MCAN Vs DCAN Transmit Procedure

Transmitting data

```

1//

2// Defines

3//

4 #define MSG DATA LENGTH

4

5 #define TX_MSG_OBJ_ID

1

6

7

uint16_t txMsgData[4];

8

9

11

// Initialize the transmit message object used for sending CAN messages.

10

11

// Message Object Parameters:

// Message Object ID Number: 1

12

13

Message Identifier: 0x1

11

14

11

Message Frame: Standard

15

11

Message Type: Transmit

11

16

Message ID Mask: 0x0

17

11

Message Object Flags: Transmit Interrupt

18

11

Message Data Length: 4 Bytes

19

11

20

CAN setupMessageObject(CANA BASE, TX MSG OBJ ID, 0x1, CAN MSG FRAME STD,

21

CAN MSG OBJ TYPE TX, 0, CAN MSG OBJ TX INT ENABLE,

MSG DATA LENGTH);

22

23

24

11

// Initialize the transmit message object data buffer to be sent

25

26

11

27

txMsgData[0] = 0x12;

28

txMsgData[1] = 0x34;

29

txMsgData[2] = 0x56;

txMsgData[3] = 0x78;

30

31

32

CAN sendMessage(CANA BASE, TX MSG OBJ ID, MSG DATA LENGTH, txMsgData);

33

```

## Figure 7-1. Transmission with DCAN

## 7.3 MCAN Transmit Concepts

This section outlines the additional features in MCAN.

- Each Tx Message can be configured to transmit in Classic CAN or CAN-FD mode

- Transmit Pause

- Transmit Cancellation

- Tx FIFO / Tx Queue

Within the Message RAM, the Tx Buffer space can have the following possible configurations:

- 1. Only Tx Buffers

- 2. Tx Buffers + Tx FIFO

- 3. Tx Buffers + Tx Queue

How to configure each of these sections has been displayed in Table 7-2 below:

| Tx Buffers           | Tx Buffers + Tx FIFO   | Tx Buffers + Tx Queue |  |

|----------------------|------------------------|-----------------------|--|

| txBufNum = BUFF_SIZE | txBufNum = BUFF_SIZE   | txBufNum = BUFF_SIZE  |  |

| (MCAN_TXBC.NDTB)     | (MCAN_TXBC.NDTB)       | (MCAN_TXBC.NDTB)      |  |

| txFIFOSize = 0       | txFIFOSize = FIFO_SIZE | txFIFOSize = QUE_SIZE |  |

| (MCAN_TXBC.TFQS)     | (MCAN_TXBC.TFQS)       | (MCAN_TXBC.TFQS)      |  |

|                      | txBufMode = 0          | txBufMode = 1         |  |

|                      | (MCAN_TXBC.TFQM)       | (MCAN_TXBC.TFQM)      |  |

### Table 7-2. Message RAM Configuration for Various Tx Buffer Options

The differences in functionality and potential use cases for each of the sections have been specified in Table 7-3 below:

| Feature                                           | Tx Buffers                                                                                                                                     | Tx FIFO                                                                                                                                                                               | Tx Queue                                                                                                                                                                                  |

|---------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Information directly available to host (CPU)      | Buffer Element number is known.                                                                                                                | Only <i>Put</i> and <i>Get</i> indices<br>can be read from a register<br>( <i>MCAN_TXFQS</i> )                                                                                        | Only <i>Put</i> and <i>Get</i> indices<br>can be read from a register<br>( <i>MCAN_TXFQS</i> )                                                                                            |

| Element transmitted first                         | Element with lowest message ID                                                                                                                 | Oldest Element                                                                                                                                                                        | Element with lowest message ID                                                                                                                                                            |

| <i>Put</i> Index / <i>Get</i> Index               | Not applicable                                                                                                                                 | Put index points to where the<br>most recent frame is stored.<br>Incremented with Add Transmit<br>Request.Get index points to the<br>oldest element, which is be<br>transmitted next. | Put index points to the lowest,<br>free buffer element (within the<br>queue), where the most recent<br>frame is stored. Updated with<br>Add Transmit Request.<br>Get index is always Zero |

| Transmission of multiple<br>messages with same ID | Element with lowest buffer<br>number is transmitted                                                                                            | Oldest Element is transmitted                                                                                                                                                         | Element with lowest buffer<br>number is transmitted                                                                                                                                       |

| Full Condition                                    | Not applicable                                                                                                                                 | In case FIFO is full, no message<br>can be written unless a requested<br>transmission is completed                                                                                    | In case queue is full, no message<br>can be written unless a requested<br>transmission is completed                                                                                       |

| Tx Cancellation                                   | Possible                                                                                                                                       | Not Possible                                                                                                                                                                          | Not Possible                                                                                                                                                                              |

| Use Cases                                         | Advantage is that the application<br>knows which message ID is<br>stored in which buffer element<br>and hence, can be edited before<br>sending | Applications where frames have<br>to be transmitted in a specific<br>order, not following increasing<br>order of message IDs                                                          | Advantage is that buffer number<br>is automatically handled by the<br><i>Put index</i> . Application need not<br>track which buffer is empty based<br>on the message ID priority          |

Table 7-3. Tx Buffers Vs Tx FIFO Vs Tx Queue Feature Comparison

Transmitting data

```

1

2

3// Assuming Message RAM has been configured

4

5

MCAN TxBufElement

txMsg;

// Initialising Structure to store Transmit Message

6

uint32_t bufNum;

7

8

9

// Initialize message to transmit.

10

11

11

txMsg.id

= ((uint32_t)(0x1)) << 18U; // Identifier Value.

txMsg.rtr

12

= OU; // Transmit data frame.

= 0U; // 11-bit standard identifier. (Bit needs to be set in the case of extended identifier)

13

txMsg.xtd

= OU; // ESI bit in CAN FD format depends only on error

14

txMsg.esi

// passive flag.

15

txMsg.dlc

= 4U; // CAN + CAN FD: transmit frame has 0-8 data bytes.

16

= OU; // CAN FD frames transmitted with bit rate

17

txMsg.brs

18

// switching disabled

txMsg.fdf

= 0U; // Frame transmitted in Classic CAN format.

19

= 1U; // Store Tx events. (Generates Tx Event FIFO element on successful transmission)

20

txMsg.efc

21

txMsg.mm

= 0xAAU; // Message Marker. (Used to match with corresponding Tx Event FIFO Element)

22

23

11

24

// Data bytes.

25

11

26

txMsg.data[0] = 0x12;

27

txMsg.data[1] = 0x34;

28

txMsg.data[2] = 0x56;

29

txMsg.data[3] = 0x78;

30

31

// Write Tx Message to a dedicated Tx Buffer in the Message RAM.

32

// Note: Parameter bufNum corresponds to desired buffer number

33

34

11

35

MCAN_writeMsgRam(MCANA_DRIVER_BASE, MCAN_MEM_TYPE_BUF, bufNum, &txMsg);

36

37

11

38

// Enable Transmission interrupt. (MCAN_TXBTIE)

39

// Each Tx Buffer has a corresponding Interrupt Enable Bit

// Note: Need not be enabled for every transmission

40

41

MCAN_txBufTransIntrEnable(MCANA_DRIVER_BASE, bufNum, 1U);

42

43

44

11

45

// Add request for transmission.

46

// Note: Parameter bufNum corresponds to desired buffer number

47

11

48

MCAN_txBufAddReq(MCANA_DRIVER_BASE, bufNum);

49

50

51

// To check that the transmission has been completed (non-essential step)

52

// Bit is set in the MCAN TXBTO register corresponding to each buffer element

53

11

54

while((HWREG(MCANA_DRIVER_BASE + MCAN_TXBTO) & (uint32_t)(1 << bufNum)) = (uint32_t)(1 << bufNum))</pre>

55

{

56

}

57

```

### Figure 7-2. Transmission with MCAN

# 7.3.1 Tx Event FIFO

Tx Event FIFOs are defined structures which are stored within the Message RAM. The module can be configured to have up to 32 elements.

While the Tx Buffer holds only the message to be transmitted, the transmit status (including the message ID and timestamp) can be stored separately using the Tx Event FIFO. The Message Marker is copied from the Tx Buffer to the Tx Event FIFO element to link the Tx Event to the Tx Event FIFO Element.

This is useful in applications with a dynamically managed transmit queue, where a Tx Buffer can be overwritten with the new message immediately after a successful transmission without needing to save the transmit status from the Tx Buffer itself. For more information on how to store Tx Event FIFO elements, see the example available in *C2000ware*.

# 8 Receiving Data

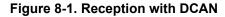

Like transmission, reception is largely identical between DCAN and MCAN. The differences stem primarily from how the Message RAM is laid out and utilized. Also, MCAN frames can be longer and employ two different bit-rates.

## 8.1 Introduction to Reception

In DCAN Message RAM, there are 32 configurable Message Objects that can be used for either transmission or reception. Receive Message Objects are used for storing received data. If needed by the application, acceptance filtering can be enabled for one or more message object(s). CPU read and write accesses to the Message RAM are done through three Interface Register (IFx) sets.

In MCAN, the Message RAM can be divided into sections to include Filter Elements, Rx Buffer Elements and Rx FIFO Elements. Filter Elements can be configured to be used with acceptance filtering and also determine where the corresponding matching frame is to be stored within the Message RAM. Rx Buffer and Rx FIFO are sections where the received frames are stored, with both having their own set of registers and interrupts. This structure provides flexibility to better serve different application needs. Message RAM can be read from directly using *Driverlib* APIs.

## 8.2 Basic Reception Process

This section outlines the high level processes involved in configuration and receiving frames using both DCAN and MCAN.

## 8.2.1 DCAN Reception

- 1. Configure Receive Message Object: This involves writing the Message IDs (ARBID) and if needed, masking for frames that are to be received.

- 2. For each received frame, the module checks against the Receive Message Objects in ascending order. On the first match, the frame is stored in the corresponding Message Object.

- 3. Either by polling or using interrupts, ascertain the reception of new data. For polling, there is a bit corresponding to each receive message object in the register *CAN\_NDAT\_21*. For using Interrupts, the procedure has been outlined in the corresponding section.

- 4. Use one of the IFx Registers to read the data from the received frame.

```

Receiving Data

```

```

1

2 #define RX MSG OBJ ID1

1

3 #define RX MSG OBJ ID2

2

4

5 uint16_t rxMsgData[4];

6

7

// Initialize the receive message object used for receiving CAN messages.

8

// Message Object Parameters:

9

11

Message Object ID Number: 1

10

11

Message Identifier: 0x4

11

Message Frame: Standard

11

12

11

Message Type: Receive

13

11

Message ID Mask: 0x0

14

11

Message Object Flags: Receive Interrupt

15

11

Message Data Length: 4 Bytes (Note that DLC field is a "don't care"

16

11

for a Receive mailbox

17

11

18

CAN setupMessageObject(CANA BASE, RX MSG OBJ ID1, 0x4, CAN MSG FRAME STD,

19

CAN MSG OBJ TYPE RX, 0, CAN MSG OBJ RX INT ENABLE,

20

0);

21

11

22

// Initialize the receive message object used for receiving CAN messages.

23

// Possible flags: CAN MSG OBJ NO FLAGS, CAN MSG OBJ USE EXT FILTER,

24

11

CAN MSG OBJ USE DIR FILTER

25

// Message Object Parameters:

Message Object ID Number: 2

26

11

27

11

Message Identifier: 0x371

28

11

Message Frame: Standard

11

29

Message Type: Receive

30

11

Message ID Mask: 0xC

31

11

Message Object Flags: UMask, MXtd, MDir

32

11

Message Object flag CAN MSG OBJ USE ID FILTER enables usage

11

33

of msgIDMask parameter for Message Identifier based filtering

Message Data Length: "Don't care" for a Receive mailbox

34

11

35

CAN setupMessageObject(CANA BASE, RX MSG OBJ ID2, 0x371,

36

CAN_MSG_FRAME_STD, CAN_MSG_OBJ_TYPE_RX, 0xC,

37

(CAN MSG OBJ USE ID FILTER | CAN MSG OBJ NO FLAGS), 0);

38

39

while(1)

40

{

41

11

42

// Read CAN message object 1 and check for new data

43

11

44

if (CAN_readMessage(myCAN0_BASE, 1, rxMsgData))

45

{

46

rxMsgCount1++;

47

}

48

11

// Read CAN message object 2 and check for new data

49

50

11

51

else if (CAN_readMessage(myCAN0_BASE, 2, rxMsgData))

52

{

53

rxMsgCount2++;

54

}

55

}

- -

```

## 8.2.2 MCAN Reception

- Configure Filter Element Size (total number), Rx Buffer size and Rx FIFO size as well as the Element Size for both Buffer and FIFO. Element Size can be configured based on the estimated data size per frame. These steps are completed as part of the Message RAM configuration. Configure Filter Elements which includes setting the Message IDs / filtering conditions desired, along with configuring where the matching frame for each corresponding Filter Element is stored (among Rx Buffer and Rx FIFO 0/1).

- 2. For each received frame, the module checks against filter elements (standard or extended, depending on the received frame) in ascending order. On getting the first match, the frame is stored as configured into the filter element. Non-matching frames can also be configured to be stored in Rx FIFO 0/1.

- 3. Either by polling or using interrupts, ascertain the reception of new data. For polling, there is a bit corresponding to each possible Rx Buffer Element in the registers *MCAN\_NDAT1* and *MCAN\_NDAT2*. Consequently, for a new message in Rx FIFO, the *MCAN\_RXFxS.FxFL* bits can be checked to get the fill level. For using Interrupts, the procedure has been outlined in the corresponding section.

- 4. Use *Driverlib* APIs to read the data from the received frame.

## **8.3 Filter Elements**

Filter Elements are defined structures, which need to be configured in the Message RAM to determine which frames are to be received and where these frames need to be stored within the Message RAM.

Standard Filter Elements are used to store Standard ID frames, and the module can be configured to have up to 128 elements. Extended Filter Elements are used to store Extended ID frames, and the module can be configured to have up to 64 elements. The structure for both Standard and Extended Filter Elements is identical except for the Message ID type. The following description given for Standard Filter Elements is valid for Extended Filter Elements as well.

The module has certain Global Filter Configurations (set in the *MCAN\_GFC* register during initialization) which determines whether to accept or reject remote frames and non-matching frames (independent configurations for both Standard and Extended IDs).

Each received frame is sequentially compared to the list of configured Filter Elements (Standard ID frames are compared to Standard Filter Elements and so on). On getting a match, based on the configuration of the corresponding filter element, the frame is accepted or rejected, and is stored in the Message RAM as configured (if accepted).

### Note:

MCAN has a separate register (*MCAN\_XIDAM*) that can be used as an Extended ID "AND" Mask. By default, the register (mask) has all bits set to one, which disables the mask.