# TMS320x280x, 2801x, 2804x DSP アナログ・デジタル・コンバータ(ADC)

# リファレンス・ガイド

2007 DSP Products

JAJU061

この資料は、Texas Instruments Incorporated (TI) が英文で記述した資料を、皆様のご理解の一助として頂くために日本テキサス・インスツルメンツ (日本 TI) が英文から和文へ翻訳して作成したものです。 資料によっては正規英語版資料の更新に対応していないものがあります。日本 TIIによる和文資料は、あくまでも TI 正規英語版をご理解頂くための補助的参考資料としてご使用下さい。 製品のご検討およびご採用にあたりましては必ず正規英語版の最新資料をご確認下さい。 TI および日本 TI は、正規英語版にて更新の情報を提供しているにもかかわらず、更新以前の情報に基づいて発生した問題や障害等につきましては如何なる責任も負いません。

# ご注意

日本テキサス・インスツルメンツ株式会社(以下TIJといいます)及びTexas Instruments Incorporated (TIJの親会社、以下TIJないしTexas Instruments Incorporatedを総称してTIといいます)は、その製品及びサービスを任意に修正し、改善、改良、その他の変更をし、もしくは製品の製造中止またはサービスの提供を中止する権利を留保します。従いまして、お客様は、発注される前に、関連する最新の情報を取得して頂き、その情報が現在有効かつ完全なものであるかどうかご確認下さい。全ての製品は、お客様とTIJとの間に取引契約が締結されている場合は、当該契約条件に基づき、また当該取引契約が締結されていない場合は、ご注文の受諾の際に提示されるTIJの標準販売契約約款に従って販売されます。

TIは、そのハードウェア製品が、TIの標準保証条件に従い販売時の仕様に対応した性能を有していること、またはお客様とTIJとの間で合意された保証条件に従い合意された仕様に対応した性能を有していることを保証します。検査およびその他の品質管理技法は、TIが当該保証を支援するのに必要とみなす範囲で行なわれております。各デバイスの全てのパラメーターに関する固有の検査は、政府がそれ等の実行を義務づけている場合を除き、必ずしも行なわれておりません。

TIは、製品のアプリケーションに関する支援もしくはお客様の製品の設計について責任を負うことはありません。TI製部品を使用しているお客様の製品及びそのアプリケーションについての責任はお客様にあります。TI製部品を使用したお客様の製品及びアプリケーションについて想定されうる危険を最小のものとするため、適切な設計上および操作上の安全対策は、必ずお客様にてお取り下さい。

TIは、TIの製品もしくはサービスが使用されている組み合せ、機械装置、もしくは方法に関連しているTIの特許権、著作権、回路配置利用権、その他のTIの知的財産権に基づいて何らかのライセンスを許諾するということは明示的にも黙示的にも保証も表明もしておりません。TIが第三者の製品もしくはサービスについて情報を提供することは、TIが当該製品もしくはサービスを使用することについてライセンスを与えるとか、保証もしくは是認するということを意味しません。そのような情報を使用するには第三者の特許その他の知的財産権に基づき当該第三者からライセンスを得なければならない場合もあり、またTIの特許その他の知的財産権に基づきTIからライセンスを得て頂かなければならない場合もあります。

TIのデータ・ブックもしくはデータ・シートの中にある情報を複製することは、その情報に一切の変更を加えること無く、かつその情報と結び付られた全ての保証、条件、制限及び通知と共に複製がなされる限りにおいて許されるものとします。当該情報に変更を加えて複製することは不公正で誤認を生じさせる行為です。TIは、そのような変更された情報や複製については何の義務も責任も負いません。

TIの製品もしくはサービスについてTIにより示された数値、特性、条件その他のパラメーターと異なる、あるいは、それを超えてなされた説明で当該TI製品もしくはサービスを再販売することは、当該TI製品もしくはサービスに対する全ての明示的保証、及び何らかの黙示的保証を無効にし、かつ不公正で誤認を生じさせる行為です。TIは、そのような説明については何の義務も責任もありません。

TIは、TIの製品が、安全でないことが致命的となる用途ないしアプリケーション(例えば、生命維持装置のように、TI製品に不良があった場合に、その不良により相当な確率で死傷等の重篤な事故が発生するようなもの)に使用されることを認めておりません。但し、お客様とTIの双方の権限有る役員が書面でそのような使用について明確に合意した場合は除きます。たとえTIがアプリケーションに関連した情報やサポートを提供したとしても、お客様は、そのようなアプリケーションの安全面及び規制面から見た諸問題を解決するために必要とされる専門的知識及び技術を持ち、かつ、お客様の製品について、またTI製品をそのような安全でないことが致命的となる用途に使用することについて、お客様が全ての法的責任、規制を遵守する責任、及び安全に関する要求事項を満足させる責任を負っていることを認め、かつそのことに同意します。さらに、もし万一、TIの製品がそのような安全でないことが致命的となる用途に使用されたことによって損害が発生し、TIないしその代表者がその損害を賠償した場合は、お客様がTIないしその代表者にその全額の補償をするものとします。

TI製品は、軍事的用途もしくは宇宙航空アプリケーションないし軍事的環境、航空宇宙環境にて使用されるようには設計もされていませんし、使用されることを意図されておりません。但し、当該TI製品が、軍需対応グレード品、若しくは「強化プラスティック」製品としてTIが特別に指定した製品である場合は除きます。TIが軍需対応グレード品として指定した製品のみが軍需品の仕様書に合致いたします。お客様は、TIが軍需対応グレード品として指定していない製品を、軍事的用途もしくは軍事的環境下で使用することは、もっぱらお客様の危険負担においてなされるということ、及び、お客様がもっぱら責任をもって、そのような使用に関して必要とされる全ての法的要求事項及び規制上の要求事項を満足させなければならないことを認め、かつ同意します。

TI製品は、自動車用アプリケーションないし自動車の環境において使用されるようには設計されていませんし、また使用されることを意図されておりません。但し、TIがISO/TS 16949の要求事項を満たしていると特別に指定したTI製品は除きます。お客様は、お客様が当該TI指定品以外のTI製品を自動車用アプリケーションに使用しても、TIは当該要求事項を満たしていなかったことについて、いかなる責任も負わないことを認め、かつ同意します。

Copyright © 2007, Texas Instruments Incorporated 日本語版 日本テキサス・インスツルメンツ株式会社

#### 弊社半導体製品の取り扱い・保管について

半導体製品は、取り扱い、保管・輸送環境、基板実装条件によっては、お客様での実装前後に破壊/劣化、または故障を起こすことがあります。

弊社半導体製品のお取り扱い、ご使用にあたっては下記の点を遵守して下さい。

#### 1. 静電気

- 素手で半導体製品単体を触らないこと。どうしても触る必要がある場合は、リストストラップ等で人体からアースをとり、導電性手袋等をして取り扱うこと。

- 弊社出荷梱包単位(外装から取り出された内装及び個装)又は製品 単品で取り扱いを行う場合は、接地された導電性のテーブル上で(導 電性マットにアースをとったもの等)、アースをした作業者が行う こと。また、コンテナ等も、導電性のものを使うこと。

- マウンタやはんだ付け設備等、半導体の実装に関わる全ての装置類は、静電気の帯電を防止する措置を施すこと。

- 前記のリストストラップ・導電性手袋・テーブル表面及び実装装置 類の接地等の静電気帯電防止措置は、常に管理されその機能が確認 されていること。

#### 2. 温·湿度環境

■ 温度:0~40℃、相対湿度:40~85%で保管・輸送及び取り扱いを行うこと。(但し、結露しないこと。)

- 直射日光があたる状態で保管・輸送しないこと。

- 3. 防湿梱包

- 防湿梱包品は、開封後は個別推奨保管環境及び期間に従い基板実装すること。

- 4. 機械的衝撃

- 梱包品(外装、内装、個装)及び製品単品を落下させたり、衝撃を 与えないこと。

- 5. 熱衝撃

- はんだ付け時は、最低限260℃以上の高温状態に、10秒以上さら さないこと。(個別推奨条件がある時はそれに従うこと。)

- 6. 汚染

- はんだ付け性を損なう、又はアルミ配線腐食の原因となるような汚染物質(硫黄、塩素等ハロゲン)のある環境で保管・輸送しないこと。

- はんだ付け後は十分にフラックスの洗浄を行うこと。(不純物含有率が一定以下に保証された無洗浄タイプのフラックスは除く。)

以上

# 以下余白

|   | 最初  | こお読みください                                                           | 9  |

|---|-----|--------------------------------------------------------------------|----|

| 1 | アナ  | ログ・デジタル・コンパータ(ADC)                                                 | 13 |

|   | 1.1 | 機能                                                                 | 14 |

|   | 1.2 | 自動変換シーケンサの動作原理                                                     | 16 |

|   |     | 1.2.1 連続サンプリング・モード                                                 | 17 |

|   |     | 1.2.2 同時サンプリング・モード                                                 | 18 |

|   | 1.3 | 割り込みなしのオートシーケンス・モード                                                | 23 |

|   |     | 1.3.1 シーケンサの開始 / 停止モード(複数のタイム・シーケンス・トリガを使用する<br>シーケンサの開始 / 停止動作)25 |    |

|   |     | 1.3.2 同時サンプリング・モード                                                 | 27 |

|   |     | 1.3.3 入力トリガの説明                                                     | 27 |

|   |     | 1.3.4 シーケンス変換中の割り込み動作                                              | 28 |

|   | 1.4 | ADC クロック・プリスケーラ                                                    | 30 |

|   |     | 1.4.1 ADC モジュールのクロックおよびサンプル・レート                                    | 30 |

|   | 1.5 | 低電力モード                                                             | 30 |

|   | 1.6 | 電源投入シーケンス                                                          | 31 |

|   | 1.7 | シーケンサ・オーバーライド機能                                                    | 31 |

|   | 1.8 | 内部 / 外部リファレンス電圧の選択                                                 | 32 |

|   | 1.9 | オフセット誤り訂正                                                          | 33 |

| 2 | ADC | レジスタ                                                               | 35 |

|   | 2.1 | ADC 制御レジスタ                                                         | 36 |

|   | 2.2 | 最大変換チャネル・レジスタ(ADCMAXCONV)                                          | 40 |

|   | 2.3 | オートシーケンス・ステータス・レジスタ(ADCASEQSR)                                     | 42 |

|   | 2.4 | ADC ステータス・フラグ・レジスタ(ADCST)                                          | 43 |

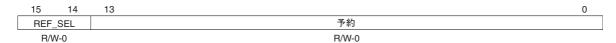

|   | 2.5 | ADC リファレンス選択レジスタ(ADCREFSEL)                                        | 44 |

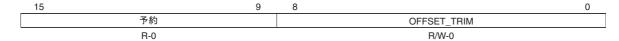

|   | 2.6 | ADC オフセット・トリム・レジスタ(ADCOFFTRIM)                                     | 44 |

|   | 2.7 | ADC 入力チャネル選択シーケンス制御レジスタ                                            | 44 |

|   | 2.8 | ADC 変換結果バッファ・レジスタ(ADCRESULTn)                                      | 45 |

# 図目次

| 1-1  | ADC モジュールのブロック図                                           | 15 |

|------|-----------------------------------------------------------|----|

| 1-2  | 連続サンプリング・モード(SMODE = 0)                                   | 17 |

| 1-3  | 同時サンプリング・モード(SMODE=1)                                     | 18 |

| 1-4  | カスケード・モードのオートシーケンス ADC のブロック図                             | 19 |

| 1-5  | デュアル・シーケンサを使用するオートシーケンス ADC のブロック図                        | 20 |

| 1-6  | 割り込みなしオートシーケンス・モードのフロー・チャート                               | 25 |

| 1-7  | シーケンサを開始する ePWM トリガの例                                     | 26 |

| 1-8  | シーケンス変換中の割り込み動作                                           | 29 |

| 1-9  | ADC コア・クロックとサンプル・ホールド(S/H)クロック                            | 30 |

| 1-10 | ADC へのクロック・チェーン                                           | 30 |

| 1-11 | 2.048-V 外部リファレンスの外部バイアス                                   | 32 |

| 1-12 | オフセット誤り訂正プロセスのフロー・チャート                                    | 33 |

| 1-13 | サンプリングされた 0-V リファレンスの最適なコード分布                             | 34 |

| 2-1  | ADC 制御レジスタ 1(ADCTRL1)(アドレス・オフセット 00h)                     | 36 |

| 2-2  | ADC 制御レジスタ 2(ADCTRL2)(アドレス・オフセット 01h)                     | 37 |

| 2-3  | ADC 制御レジスタ 3(ADCTRL3)(アドレス・オフセット 18h)                     | 39 |

| 2-4  | 最大変換チャネル・レジスタ(ADCMAXCONV)(オフセット・アドレス 02h)                 | 40 |

| 2-5  | オートシーケンス・ステータス・レジスタ(ADCASEQSR)(アドレス・オフセット 07h)            | 42 |

| 2-6  | ADC ステータス・フラグ・レジスタ(ADCST)(アドレス・オフセット 19h)                 | 43 |

| 2-7  | ADC リファレンス選択レジスタ(ADCREFSEL)(アドレス・オフセット 1Ch)               | 44 |

| 2-8  | ADC オフセット・トリム・レジスタ(ADCOFFTRIM)(アドレス・オフセット 1Dh)            | 44 |

| 2-9  | ADC 入力チャネル選択シーケンス制御レジスタ(ADCCHSELSEQ1)<br>(アドレス・オフセット 03h) | 44 |

| 2-10 | ADC 入力チャネル選択シーケンス制御レジスタ(ADCCHSELSEQ2)<br>(アドレス・オフセット 04h) | 44 |

| 2-11 | ADC 入力チャネル選択シーケンス制御レジスタ(ADCCHSELSEQ3)<br>(アドレス・オフセット 05h) | 45 |

| 2-12 | ADC 入力チャネル選択シーケンス制御レジスタ(ADCCHSELSEQ4)<br>(アドレス・オフセット 06h) | 45 |

| 2-13 | ADC 変換結果バッファ・レジスタ(ADCRESULTn)-(アドレス 0x7108 ~ 0x7117)      |    |

| 2-14 | ADC 変換結果バッファ・レジスタ(ADCRESULTn)-(アドレス 0x0B00 ~ 0x0B0F)      | 46 |

# 表目次

| 1-1  | ADC レジスタ                                | 15 |

|------|-----------------------------------------|----|

| 1-2  | 単一動作モードとカスケード動作モードの比較                   | 21 |

| 1-3  | ADCCHSELSEQn レジスタの値(MAX_CONV1 を 6 にセット) | 24 |

| 1-4  | ADCCHSELSEQn の値(MAX_CONV1 を 2 にセット)     | 27 |

| 1-5  | 第2の自動変換セッション後の値                         | 27 |

| 1-6  | 入力トリガ                                   | 27 |

| 1-7  | ADC へのクロック・チェーン                         | 30 |

| 1-8  | 電力オプション                                 | 31 |

| 2-1  | ADC 制御レジスタ 1(ADCTRL1)のフィールドの説明          | 36 |

| 2-2  | ADC 制御レジスタ 2(ADCTRL2)のフィールドの説明          | 37 |

| 2-3  | ADC 制御レジスタ 3(ADCTRL3)のフィールドの説明          | 39 |

| 2-4  | 最大変換チャネル・レジスタ(ADCMAXCONV)のフィールドの説明      | 41 |

| 2-5  | さまざまな数の変換の MAX_CONV1 のビット選択             | 41 |

| 2-6  | オートシーケンス・ステータス・レジスタ(ADCASEQSR)のフィールドの説明 | 42 |

| 2-7  | アクティブ・シーケンサの状態                          | 42 |

| 2-8  | ADC ステータス・フラグ・レジスタ(ADCST)のフィールドの説明      | 43 |

| 2-9  | ADC リファレンス選択レジスタ(ADCREFSEL)のフィールドの説明    | 44 |

| 2-10 | ADC オフセット・トリム・レジスタ(ADCOFFTRIM)のフィールドの説明 | 44 |

| 2-11 | CONVnn ビット値および選択される ADC 入力チャネル          | 45 |

# 最初にお読みください

#### 本書について

本書では、TMS320x280x、2801x、および 2804x デジタル・シグナル・プロセッサ (DSP) で利用できるアナログ・デジタル・コンバータ (ADC) の機能と動作について説明します。

#### 表記規則

本書では、次の表記規則を使用しています。

- デバイス番号 TMS320x280x は、多くの場合 280x のように省略されます。

- 16 進数は末尾に h が付いて表されています。たとえば、40h は 16 進数の 40(10 進数の 64)です。同様に、2 進数は通常、末尾に b が付いて表されています。 たとえば、0100b は 10 進数の 4 を 2 進数で示したものです。

- 本書内のレジスタは、図に示され、表で説明されます。

- 各レジスタ図は、長方形で分割されたレジスタのフィールドを表します。 各フィールドには、ビット名のラベルが付けられます。開始および終了ビット番号は上に、リード/ライト・プロパティは下にあります。説明文は、プロパティに対して使用される表記を説明します。

- レジスタ図の予約ビットは、アプリケーションに使用できないビットを示します。

- 信号がロー・アクティブの場合は、上線が付いています。たとえば、ARS 信号はロー・アクティブです。

#### 関連資料

280x デバイスおよびそのサポート・ツールなどを解説した関連資料は、以下のとおりです。以下の資料のコピーは www.ti.com で入手できます。 *ヒント*: www.ti.com に表示される検索ボックスに文書番号を入力してください。

#### データ・マニュアル —

**SPRS230:—\_『TMS320F2809,F2808, F2806, F2802, F2801, F2801x UCD9501, C2802, C2801 DSPs**<u>Data Manual</u> には、F280x デバイスのピンアウト、信号表記、電気的仕様およびタイミング仕様が含まれています。

**SPRS357:**—<u>『TMS320F28044 Digital Signal Processor Data Manual』</u>には、F28044 デバイスのピンアウト、信号表記、電気的仕様およびタイミング仕様が含まれています。

#### ユーザーズ・ガイド—

SPRU051:—『TMS320x28xx、28xxx Serial Communication Interface (SCI) Reference Guide』では、UART として一般的に知られる SCI (2 線式非同期シリアル・ポート) について説明しています。SCI モジュールは、標準 NRZ (non-return-to-zero) フォーマットを使用する CPU と他の非同期ペリフェラルの間のデジタル通信をサポートします。

SPRU059:—<u>『TMS320x28xx, 28xxx Serial Peripheral Interface (SPI) Reference Guide</u>』では、SPI(高速同期シリアル入力/出力(I/O)ポート)について説明しています。このポートにより、プログラムされた長さ(1 ~ 16 ビット)のシリアル・ビット・ストリームを、プログラムされたビット転送レートで送受信することができます。

- SPRU074:—『TMS320x28xx, 28xxx Enhanced Controller Area Network (eCAN) Reference Guide』では、確立されたプロトコルを使用して電気的にノイズの多い環境で他のコントローラと逐次的に通信する eCAN について説明しています。

- SPRU430:—『TMS320C28x DSP CPU and Instruction Set Reference Guide』では、中央演算処理ユニット(CPU)と、TMS320C28x 固定小数点デジタル・シグナル・プロセッサ(DSP)の命令セットについて説明しています。また、これらの DSP で利用できるエミュレーション機能についても説明します。

- **SPRU513:—『TMS320C28x Assembly Language Tools User's Guide』**では、TMS320C28x デバイス用のアセンブリ言語ツール(アセンブリ言語コードの開発に使用するアセンブラなどのツール)、アセンブラ擬似命令、マクロ、共通オブジェクト・ファイル・フォーマット、およびシンボリック・デバッグの擬似命令について説明しています。

- SPRU514:—<u>『TMS320C28x Optimizing C Compiler User's Guide</u>』では、TMS320C28x™ C/C++ コンパイラについて説明しています。このコンパイラは、ANSI 標準 C/C++ ソース・コードを受け、TMS320C28x デバイス用の TMS320 DSP アセンブリ言語ソース・コードを生成します。

- **SPRU566:—『TMS320x28xx, 28xxx Peripheral Reference Guide』**には、28x デジタル・シグナル・プロセッサ (DSP) のペリフェラル・リファレンス・ガイドが記載されています。

- SPRU608:—<u>『The TMS320C28x Instruction Set Simulator Technical Overview』</u>では、C28x™ コアの命令セットをシミュレートするシミュレータ(TMS320C2000 IDE 用の Code Composer Studio 内で利用可能)について説明しています。

- SPRU625:— 『TMS320C28x DSP/BIOS Application Programming Interface (API) Reference Guide』では、DSP/BIOS を使用した開発について説明します。

- **SPRU712:—『TMS320x28xx, 28xxx System Control and Interrupts Reference Guide』**では、280x デジ タル・シグナル・プロセッサ (DSP) のさまざまな割り込みとシステム制御機能について説明します。

- **SPRU721:**—<u>『TMS320x28xx. 28xxx Inter-Integrated Circuit (I2C) Reference Guide』</u>では、TMS320x280x デジタル・シグナル・プロセッサ(DSP)で利用できる Inter-Integrated Circuit(I<sup>2</sup>C)モジュールの機能と動作について説明しています。

- SPRU722:—<u>『TMS320x280x, 2801x, 2804x Boot ROM Reference Guide』</u>では、ブートローダ(工場でプログラムされたブート・ローディング・ソフトウェア)の用途と機能について説明しています。また、デバイス・オンチップ・ブート ROM の他の内容についても説明し、そのメモリ内のどこに情報のすべてが配置されているかを示します。

- **SPRU790:**—『TMS320x28xx、28xxx Enhanced Quadrature Encoder Pulse (eQEP) Reference Guide』では、eQEP モジュールについて説明しています。高性能のモーションおよび位置制御システムでは、このモジュールをリニアまたはロータリ・インクリメンタル・エンコーダとのインターフェイスに使用して、位置、方向、および速度情報をエンコーダから取得します。この資料には、モジュールとレジスタの説明が含まれます。

- **SPRU791:—『TMS320x28xx, 28xxx Enhanced Pulse Width Modulator (ePWM) Module Reference**<u>Guide』</u>では、デジタル・モータ制御、スイッチ・モード電源制御、UPS(無停電電源装置)、他の形式の電源変換など、エンハンスド PWM モジュールについて説明しています。

- SPRU807:—<u>『TMS320x28xx, 28xxx Enhanced Capture (eCAP) Module Reference Guide</u>』では、エンハンスド・キャプチャ・モジュールについて説明しています。この資料には、モジュールとレジスタの説明が含まれます。

- **SPRU924:**—<u>『TMS320x28xx, 28xxx High-Resolution Pulse Width Modulator (HRPWM)</u>』では、PWM モジュールに追加された高分解能 PWM (HRPWM) の動作について説明しています。

#### アプリケーション・レポート--

- **SPRAA58:—『TMS320x281x to TMS320x280x Migration Overview』**では、TI の TMS320x281x DSP と TMS320x280x DSP の違いを説明して、281x から 280x へのアプリケーション移行を支援します。本書の主な焦点は 281x から 280x への移行ですが、反対の移行(280x から 281x へ)を検 討しているユーザーにも役立ちます。

- SPRA550:— <u>『3.3 V DSP for Digital Motor Control』</u>では、3.3V 専用モータ・コントローラのシナリオについて説明し、ほとんどのアプリケーションについて 3.3V ~ 5V 間のインターフェイスの重要な問題が存在しないことを示します。オンチップ 3.3V アナログ・デジタル・コンバータ(ADC)と 5V ADC についても説明します。

- システム・ノイズと EMI 効果を低減できるコンポーネント・レイアウトとプリント回路基板 (PCB) 設計のガイドラインが要約されています。

- SPRA820:—『Online Stack Overflow Detection on the TMS320C28x DSP』では、TMS320C28x™ DSP でのオンライン・スタック・オーバーフロー検出の方法論を示します。DSP/BIOS™ アプリケーションと非DSP/BIOSアプリケーションの両方でオーバーフロー検出を実装するための関数が含まれている C ソース・コードが提供されます。

- **SPRA861:—**『RAMDISK: A Sample User-Defined C I/O Driver』では、任意のデバイスでハイレベルな CIO 機能の高度なバッファリングを使用するための簡単な方法を提供します。このアプリケー ション・レポートは、ユーザー定義デバイス・ドライバのサンプル実装を示します。

- SPRA873:—『Thermo-Electric Cooler Control Using a TMS320F2812 DSP & DRV592 Power Amplifier』では、テキサス・インスツルメンツの TMS320F2812 デジタル・シグナル・プロセッサ (DSP) と DRV592 パワー・アンプで構成される電子冷却システムを示します。DSP は、内蔵の 12 ビットアナログ・デジタル・コンバータを使用して (サーミスタの値をリードし)、H ブリッジ DRV592 パワー・アンプへのパルス幅変調波形の直接出力でデジタル比例 / 積分 / 微分フィードバック・コントローラを実装します。ソフトウェアおよびソフトウェア操作手順と共に実験システムの完全な説明が提供されます。

- SPRA876:—『Programming Examples for the TMS320F281x eCAN』には、複数のプログラミング例が 含まれており、eCAN モジュールが各種動作モードについてどのように設定され、eCAN の迅速 なプログラミングに役立つかを示しています。プロジェクトと CANalyzer 設定ファイルは、付属の SPRA876.zip ファイルにすべて含まれています。

- SPRA953:—<u>『IC Package Thermal Metrics』</u>では、従来と新規のサーマル・メトリックスについて説明し、各種アプリケーションをシステム・レベル・ジャンクション温度推定に関連づけて取り上げます。

- SPRA958:— 『Running an Application from Internal Flash Memory on the TMS320F281x DSP (Rev. B)』 では、オンチップ・フラッシュ・メモリからの実行について、アプリケーション・ソフトウェア を正しく設定するために必要な要件を扱います。DSP/BIOS™ と非 DSP/BIOS プロジェクトの両方に対する要件が示されます。コード・プロジェクト例が含まれています。

- **SPRA963:—** <u>『Reliability Data for TMS320LF24x and TMS320F281x Devices</u>』では、TMS320LF24x および TMS320F281x デバイスの信頼性データについて説明しています。

- **SPRA989:—『F2810**, F2811, and F2812 ADC Calibration』では、F2810/F2811/F2812 デバイスに搭載されている 12 ビット・アナログ・デジタル・コンバータ(ADC)の絶対精度を向上させる方法について説明しています。 このアプリケーション・ノートには、F2812 eZdsp の RAM から実行するプログラム例

- このアプリケーション・ノートには、F2812 eZdsp の RAM から実行するプログラム例 (ADCcalibration.zip)が付属しています。

- SPRA991:— <u>『Simulation Fulfills its Promise for Enhancing Debug and Analysis A White Paper』</u>では、より効果的に代替システムを評価できるようにすることによって開発者の開発サイクルの短縮を可能する拡張されたシミュレーションについて説明しています。

#### 商標

TMS320C28x、C28x は、テキサス・インスツルメンツの商標です。

# アナログ・デジタル・コンバータ (ADC)

TMS320x280x ADC モジュールは 12 ビット・パイプライン・アナログ・デジタル・コンバータ(ADC)です。

本章でコアと呼ばれるこのコンバータのアナログ回路には、フロントエンド・アナログ・マルチプレクサ(MUX)、サンプル・ホールド(S/H)回路、変換コア、電圧レギュレータ、およびその他のアナログ・サポート回路が含まれます。本書でラッパーと呼ばれるデジタル回路には、プログラマブル変換シーケンサ、リザルト・レジスタ、アナログ回路へのインターフェイス、デバイス・ペリフェラル・バスへのインターフェイス、およびその他のオンチップ・モジュールへのインターフェイスが含まれます。

このリファレンス・ガイドは、TMS320x280x ファミリのプロセッサに搭載されている ADC に適用できます。これには、280x ファミリ内のフラッシュベース、ROM ベース、および RAM ベースのデバイスがすべて含まれます。

項目 ページ 1.1 1.2 自動変換シーケンサの動作原理 ......16 1.3 ADC クロック・プリスケーラ ...... 30 1.4 1.5 1.6 電源投入シーケンス ...... 31 シーケンサ・オーバーライド機能 ......31 1.7

内部 / 外部リファレンス電圧の選択......32

オフセット誤り訂正 ...... 33

1.81.9

#### 1.1 機能

ADC モジュールは 16 チャネルで、ePWM モジュール用に 2 つの独立した 8 チャネル・モジュールとして設定可能です。2 つの独立した 8 チャネル・モジュールをカスケードにして 16 チャネル・モジュールを形成することもできます。

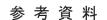

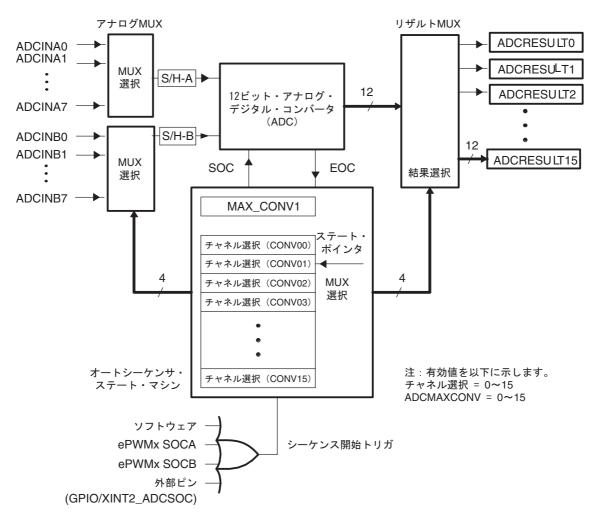

複数の入力チャネルと 2 つのシーケンサがありますが、ADC モジュールのコンバータは 1 つのみです。 図 1-1 は 280x ADC モジュールのブロック図です。

2つの8チャネル・モジュールによって一連の変換をオートシーケンスできます。各モジュールがアナログMUXを介して使用可能な対応する8チャネルのいずれかを選択します。カスケード・モードでは、オートシーケンサが単一の16ビット・チャネル・シーケンサとして機能します。変換が完了すると、選択されたチャネル値が各シーケンサの対応するADCRESULTレジスタに格納されます。

オートシーケンスによって、システムが同じチャネルを複数回変換することが可能になり、ユーザーはオーバーサンプリング・アルゴリズムを実行できます。このオーバーサンプリングによって、従来の単ーサンプリング変換結果より高い分解能を得ることができます。

ADC モジュールの機能を以下に示します。

- デュアル・サンプル・ホールド(S/H) 搭載 12 ビット ADC コア

- 同時サンプリング・モードまたは連続サンプリング・モード

- アナログ入力: 0V ~ 3V

- 12.5MHz、ADC クロック、6.25MSPS の高速変換

- 16 チャネル、マルチプレクス入力

- 単一セッションで最大16の自動変換を実現するオートシーケンス機能。1~16の入力チャネルのいずれかを選択するように各変換をプログラム可能

- シーケンサは2つの独立した8ステート・シーケンサまたは1つの大きな16ステート・シーケンサ(2 つのカスケード8ステート・シーケンサ)として動作可能

- 16 のリザルト・レジスタ (個々にアドレス指定可能) に変換値を格納

1 + = 1 = K\*\* F. ADOLO

0V < 入力 < 3V の場合

デジタル値 = 4095、

入力値≥3V の場合

- 小数点以下切り捨て

- 変換開始 (SOC) シーケンスのソースとして複数のトリガ

- S/W ソフトウェアによる即時開始

- ePWM 1 ~ 6

- GPIO XINT2

- 各シーケンス終了(EOS) または 1 つおきの EOS に対する柔軟な割り込みリクエストが可能

- シーケンサが開始 / 停止モードで動作可能、複数のタイム・シーケンス・トリガにより変換を同期

- ePWM トリガがデュアル・シーケンサ・モードで独立して動作可能

- サンプル・ホールド (S/H) 取得時間ウィンドウに個別のプリスケール制御

#### 図 1-1 ADC モジュールのブロック図

表 1-1 ADC レジスタ

| 名前           | アドレス <sup>(1)</sup> | アドレス <sup>(2)</sup> | サイズ (x16) | 説明                      |

|--------------|---------------------|---------------------|-----------|-------------------------|

| ADCTRL1      | 0x7100              |                     | 1         | ADC 制御レジスタ 1            |

| ADCTRL2      | 0x7101              |                     | 1         | ADC 制御レジスタ 2            |

| ADCMAXCONV   | 0x7102              |                     | 1         | ADC 最大変換チャネル・レジスタ       |

| ADCCHSELSEQ1 | 0x7103              |                     | 1         | ADC チャネル選択シーケンス制御レジスタ 1 |

| ADCCHSELSEQ2 | 0x7104              |                     | 1         | ADC チャネル選択シーケンス制御レジスタ 2 |

| ADCCHSELSEQ3 | 0x7105              |                     | 1         | ADC チャネル選択シーケンス制御レジスタ 3 |

| ADCCHSELSEQ4 | 0x7106              |                     | 1         | ADC チャネル選択シーケンス制御レジスタ 4 |

| ADCASEQSR    | 0x7107              |                     | 1         | ADC オートシーケンス・ステータス・レジスタ |

| ADCRESULT0   | 0x7108              | 0x0B00              | 1         | ADC 変換結果バッファ・レジスタ 0     |

| ADCRESULT1   | 0x7109              | 0x0B01              | 1         | ADC 変換結果バッファ・レジスタ 1     |

| ADCRESULT2   | 0x710A              | 0x0B02              | 1         | ADC 変換結果バッファ・レジスタ 2     |

| ADCRESULT3   | 0x710B              | 0x0B03              | 1         | ADC 変換結果バッファ・レジスタ 3     |

| ADCRESULT4   | 0x710C              | 0x0B04              | 1         | ADC 変換結果バッファ・レジスタ 4     |

| ADCRESULT5   | 0x710D              | 0x0B05              | 1         | ADC 変換結果バッファ・レジスタ 5     |

| ADCRESULT6   | 0x710E              | 0x0B06              | 1         | ADC 変換結果バッファ・レジスタ 6     |

| ADCRESULT7   | 0x710F              | 0x0B07              | 1         | ADC 変換結果バッファ・レジスタ 7     |

| ADCRESULT8   | 0x7110              | 0x0B00              | 1         | ADC 変換結果バッファ・レジスタ 8     |

| ADCRESULT9   | 0x7111              | 0x0B09              | 1         | ADC 変換結果バッファ・レジスタ 9     |

<sup>(1)</sup> この列のレジスタはペリフェラル・フレーム 2 レジスタです。

<sup>(2)</sup> ADC リザルト・レジスタは F280x DSP にデュアル・マップされます。ペリフェラル・フレーム 2 (0x7108-0x7117) の場所は 2 ウェイト・ステートおよび左詰めです。ペリフェラル・フレーム 0 空間 (0x0B00-0x0B0F) の場所は 0 ウェイト・ステートおよび右詰めです。ADC を高速 / 連続変換に使用するときは、ADC 変換が欠けることを回避するために 0 ウェイト・ステート の場所を使用します。

表 1-1 ADC レジスタ (続き)

| 名前          | アドレス <sup>(1)</sup> | アドレス <sup>(2)</sup> | サイズ (x16) | 説明                   |

|-------------|---------------------|---------------------|-----------|----------------------|

| ADCRESULT10 | 0x7112              | 0x0B0A              | 1         | ADC 変換結果バッファ・レジスタ 10 |

| ADCRESULT11 | 0x7113              | 0x0B0B              | 1         | ADC 変換結果バッファ・レジスタ 11 |

| ADCRESULT12 | 0x7114              | 0x0B0C              | 1         | ADC 変換結果バッファ・レジスタ 12 |

| ADCRESULT13 | 0x7115              | 0x0B0D              | 1         | ADC 変換結果バッファ・レジスタ 13 |

| ADCRESULT14 | 0x7116              | 0x0B0E              | 1         | ADC 変換結果バッファ・レジスタ 14 |

| ADCRESULT15 | 0x7117              | x0B0F               | 1         | ADC 変換結果バッファ・レジスタ 15 |

| ADCTRL3     | 0x7118              |                     | 1         | ADC 制御レジスタ 3         |

| ADCST       | 0x7119              |                     | 1         | ADC ステータス・レジスタ       |

| 予約          | 0x711A<br>0x711B    |                     | 2         |                      |

| ADCREFSEL   | 0x711C              |                     | 1         | ADC リファレンス・セレクト・レジスタ |

| ADCOFFTRIM  | 0x711D              |                     | 1         | ADC オフセット・トリム・レジスタ   |

| 予約          | 0x711E<br>0x711F    |                     | 2         | ADC ステータス・レジスタ       |

ADC の仕様どおりの精度を得るには、適したボード・レイアウトが非常に重要です。できる限り、ADCINxx ピンにつながるトレースがデジタル信号パスに近接しないようにしてください。

これは、ADC 入力に結合することによるデジタル・ラインのスイッチング・ノイズを最小限に抑えるためです。

さらに、正しい絶縁手法を用いて ADC モジュールの電源ピンをデジタル電源から絶縁する必要があります。

# 1.2 自動変換シーケンサの動作原理

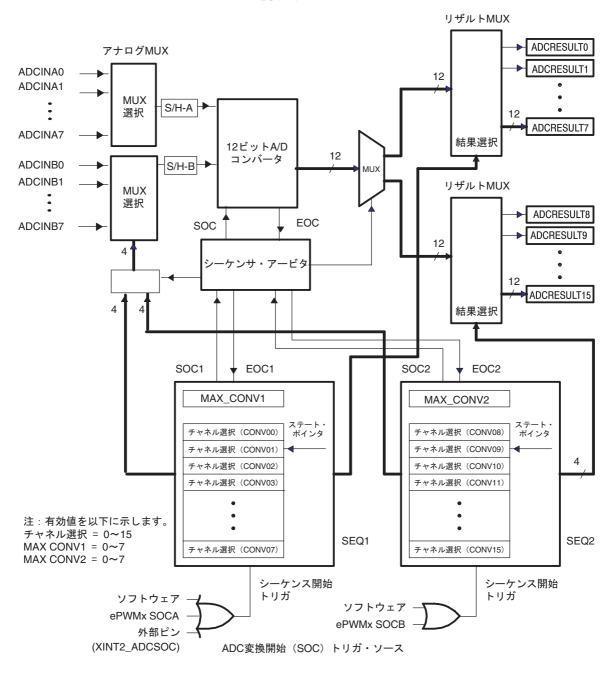

ADC シーケンサは 2 つの独立した 8 ステート・シーケンサ (SEQ1 と SEQ2) から構成され、これらをカスケードにして 1 つの 16 ステート・シーケンサ (SEQ) を形成することもできます。" ステート " という語は、シーケンサで実行できる自動変換の数を表します。シングル (16 ステート、カスケード) およびデュアル (8 ステート 2 つ、独立) シーケンサ・モードのブロック図をそれぞれ図 1-4 および図 1-5 に示します。

両方とも ADC が一連の変換をオートシーケンスすることができます。つまり、ADC は変換開始リクエストを受け取るたびに、複数の変換を自動的に実行できます。

それぞれの変換に対して、使用可能な 16 入力チャネルのいずれかをアナログ MUX を介して選択できます。変換後、選択されたチャネルのデジタル値が適切なリザルト・レジスタに格納されます (ADCRESULTn)。最初の結果が ADCRESULT0 に、2 番目の結果が ADCRESULT1 に (以下同様) 格納されます。同じチャネルを複数回サンプリングすることも可能なため、ユーザーがオーバーサンプリングを実行して、従来の単一サンプリングによる変換結果より高い分解能を得ることもできます。

注: 連続サンプリング・デュアル・シーケンサ・モードでは、現在アクティブなシーケンサによって開始されたシーケンスが終了すると、即座にいずれかのシーケンサからの保留中の SOC リクエストが取得されます。たとえば、SEQ1 の SOC リクエストが発生したときに、SEQ2 のために A/D コンバータがビジーであるとします。A/D コンバータは SEQ2 で処理中のリクエストが完了すると、即座に SEQ1 を開始します。SEQ1 と SEQ2 両方からの SOC リクエストが保留中の場合は、SEQ1 の SOC が優先されます。たとえば、SEQ1 のために A/D コンバータがビジーであるとします。このプロセス中に、SEQ1 と SEQ2 両方からの SOC リクエストが発生します。SEQ1 がアクティブなシーケンスを完了すると、SEQ1 の SOC リクエストが即座に取得されます。SEQ2 の SOC リクエストは保留されたままになります。

ADC は同時サンプリング・モードまたは連続サンプリング・モードでも動作可能です。各変換(同時サンプリング・モードの場合は変換のペア)に対して、現在の CONVxx ビット・フィールドがサンプリングと変換対象のピン(またはピンのペア)を設定します。連続サンプリング・モードでは、CONVxx の4 ビットすべてが入力ピンを設定します。MSB が、入力ピンがどのサンプル・ホールド・バッファに対応するかを設定し、3 つの LSB がオフセットを設定します。たとえば、CONVxx に値 0101b が格納さ

れている場合、選択される入力ピンは ADCINA5 です。値 1011b が格納されている場合は、選択される 入力ピンは ADCINB3 です。同時サンプリング・モードでは、CONVxx レジスタの MSB が捨てられます。CONVxx レジスタの 3 つの LSB によって設定されたオフセットに対応するピンを、各サンプル・ホールド・バッファがサンプリングします。たとえば、CONVxx レジスタに値 0110b が格納されている 場合は、S/H-A によって ADCINA6 がサンプリングされ、S/H-B によって ADCINB6 がサンプリングされます。値が 1001b の場合は、S/H-A によって ADCINA1 がサンプリングされ、S/H-B によって ADCINB1 がサンプリングされます。S/H-A の電圧が最初に変換され、続いて S/H-B の電圧が変換されます。S/H-A 変換の結果が現在の ADCRESULTn レジスタに格納されます(シーケンサがリセットされた場合、SEQ1 の場合は ADCRESULT0)。S/H-B 変換の結果が次の ADCRESULTn レジスタに格納されます(シーケンサがリセットされた場合、SEQ1 の場合は ADCRESULT2 を指す)。

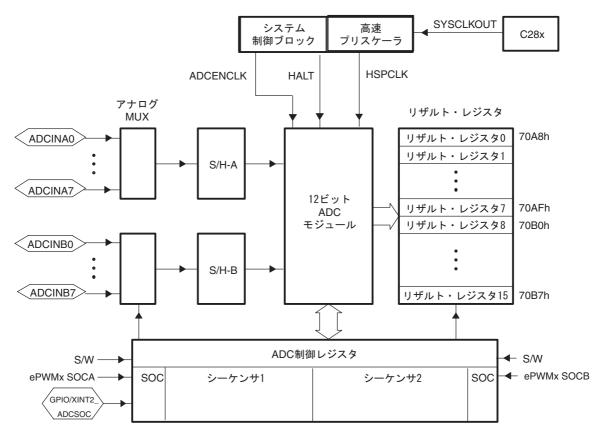

#### 1.2.1 連続サンプリング・モード

図 1-2 は連続サンプリング・モードのタイミングを示しています。この例では、ACQ\_PS ビットが 0001b にセットされています。

図 1-2 連続サンプリング・モード (SMODE = 0)

凡例: C1 - リザルト・レジスタ更新時間 S - 取得ウィンドウ

A [CONV00] 4 ビット・レジスタに格納される ADC チャネル・アドレス。SEQ1 の場合は CONV00、SEQ2 の場合は CONV08 です。

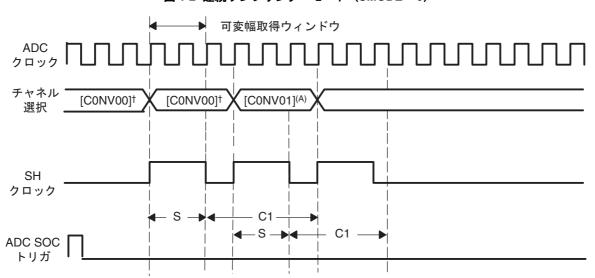

#### 1.2.2 同時サンプリング・モード

図 1-3 は同時サンプリング・モードのタイミングを示しています。この例では、 $ACQ_PS$  ビットが 0001b にセットされています。

#### 図 1-3 同時サンプリング・モード (SMODE=1)

可変幅取得ウィンドウ

凡例: C1 - リザルト・レジスタの Ax チャネル結果の存続時間 C2 - リザルト・レジスタの Bx チャネル結果の存続時間 S - 取得ウィンドウ

A [CONV00] 4 ビット・レジスタに格納される ADC チャネル・アドレス。[CONV00] は A0/B0 チャネル、[CONV01] は A1/B1 チャネルを示します。

#### 図 1-4 カスケード・モードのオートシーケンス ADC のブロック図

#### 図 1-5 デュアル・シーケンサを使用するオートシーケンス ADC のブロック図

注: DSP には ADC が 1 つのみです。デュアル・シーケンサ・モードではこのコンバータが 2 つのシーケンサによって共有されます。

8 ステート・モードと 16 ステート・モードのシーケンサの動作はほぼ同一です。わずかな差異について は表 1-2 を参照してください。

#### 表 1-2 単一動作モードとカスケード動作モードの比較

| 機能                         | 単一 8 ステート・<br>シーケンサ #1(SEQ1)   | 単一 8 ステート・<br>シーケンサ #2(SEQ2) | カスケード 16 ステート・<br>シーケンサ(SEQ)              |

|----------------------------|--------------------------------|------------------------------|-------------------------------------------|

| 変換開始(SOC)トリガ               | ePWMx SOCA、<br>ソフトウェア、<br>外部ピン | ePWMx SOCB、<br>ソフトウェア        | ePWMx SOCA、<br>ePWMx SOCB、<br>ソフトウェア、外部ピン |

| 自動変換の最大数(シーケンス長)           | 8                              | 8                            | 16                                        |

| シーケンス終了(EOS)での自動停止         | はい                             | はい                           | はい                                        |

| アービトレーション優先順位              | High                           | Low                          | 適用せず                                      |

| ADC 変換リザルト・レジスタの場所         | 0 ~ 7                          | 8 <b>~</b> 15                | 0 ~ 15                                    |

| ADCCHSELSEQn ビット・フィールド割り当て | CONV00 ~ CONV07                | CONV08 ~ CONV15              | CONV00 ~ CONV15                           |

便宜上、以降はシーケンサ状態が以下のように示されます。

SEQ1 : CONV00 ~ CONV07

SEQ2 : CONV08 ~ CONV15

カスケード SEQ: CONV00 ~ CONV15

各シーケンス変換に対して選択されるアナログ入力チャネルは、ADC 入力チャネル選択シーケンス制御レジスタ(ADCCHSELSEQn)の CONVxx ビット・フィールドで設定されます。CONVxx は 4 ビット・フィールドで、変換のために 16 チャネルのいずれかを指定します。シーケンサをカスケード・モードで使用する場合は、1 シーケンスで最大 16 変換が可能なため、16 個の 4 ビット・フィールド(CONV00~CONV15)が使用可能で、これらが 4 つの 16 ビット・レジスタに(ADCCHSELSEQ1~ADCCHSELSEQ4)配置されます。CONVxx ビットは 0~15 の任意の値を格納可能です。アナログ・チャネルは任意の必要な順序で選択でき、同じチャネルを複数回選択することもできます。

#### 例 1-1 同時サンプリング・デュアル・シーケンサ・モードの例

```

初期化の例:

AdcRegs.ADCTRL3.bit.SMODE_SEL = 0x1;

// Setup simultaneous sampling mode

0x0033;

// 4 double conv's each sequencer (8 total)

AdcRegs.ADCMAXCONV.all =

AdcRegs.ADCCHSELSEQ1.bit.CONV00 = 0x0; // Setup conv from ADCINAO & ADCINBO

AdcRegs.ADCCHSELSEQ1.bit.CONV01 = 0x1; // Setup conv from ADCINA1 & amp; ADCINB1

AdcRegs.ADCCHSELSEQ1.bit.CONV02 = 0x2;

// Setup conv from ADCINA2 & amp; ADCINB2

AdcRegs.ADCCHSELSEQ1.bit.CONV03 = 0x3; // Setup conv from ADCINA3 & amp; ADCINB3

AdcRegs.ADCCHSELSEQ3.bit.CONV08 = 0x4;

// Setup conv from ADCINA4 & amp; ADCINB4

AdcRegs.ADCCHSELSEQ3.bit.CONV09 = 0x5; // Setup conv from ADCINA5 & amp; ADCINB5

AdcRegs.ADCCHSELSEQ3.bit.CONV10 = 0x6; // Setup conv from ADCINA6 & amp; ADCINB6

AdcRegs.ADCCHSELSEQ3.bit.CONV11 = 0x7;

// Setup conv from ADCINA7 & amp; ADCINB7

SEQ1とSEQ2の両方を実行した場合は、結果が以下のADCRESULTレジスタに格納されます。

ADCINAO -> ADCRESULTO

ADCINBO -> ADCRESULT1

ADCINA1 -> ADCRESULT2

ADCINB1 -> ADCRESULT3

ADCINA2 -> ADCRESULT4

ADCINB2 -> ADCRESULT5

ADCINA3 -> ADCRESULT6

ADCINB3 -> ADCRESULT7

ADCINA4 -> ADCRESULT8

ADCINB4 -> ADCRESULT9

ADCINA5 -> ADCRESULT10

ADCINB5 -> ADCRESULT11

ADCINA6 -> ADCRESULT12

ADCINB6 -> ADCRESULT13

ADCINA7 -> ADCRESULT14

ADCINB7 -> ADCRESULT15

```

#### 例 1-2 同時サンプリング・カスケード・シーケンサ・モードの例

```

AdcRegs.ADCTRL3.bit.SMODE SEL =

0x1:

// Setup simultaneous sampling mode

AdcRegs.ADCTRL1.bit.SEQ CASC

0x1;

// Setup cascaded sequencer mode

AdcRegs.ADCMAXCONV.all =

0x0007; // 8 double conv's (16 total)

AdcReqs.ADCCHSELSEQ1.bit.CONV00

= 0x0; // Setup conv from ADCINAO & amp; ADCINBO

AdcRegs.ADCCHSELSEQ1.bit.CONV01

= 0x1; // Setup conv from ADCINA1 & amp; ADCINB1

= 0x2; // Setup conv from ADCINA2 & amp; ADCINB2

AdcRegs.ADCCHSELSEQ1.bit.CONV02

AdcRegs.ADCCHSELSEQ1.bit.CONV03

= 0x3; // Setup conv from ADCINA3 & amp; ADCINB3

AdcRegs.ADCCHSELSEQ2.bit.CONV04

= 0x4; // Setup conv from ADCINA4 & amp; ADCINB4

AdcRegs.ADCCHSELSEQ2.bit.CONV05

= 0x5; // Setup conv from ADCINA5 & amp; ADCINB5

AdcRegs.ADCCHSELSEQ2.bit.CONV06

= 0x6; // Setup conv from ADCINA6 & amp; ADCINB6

AdcRegs.ADCCHSELSEQ2.bit.CONV07

= 0x7; // Setup conv from ADCINA7 & amp; ADCINB7

カスケードSEQを実行した場合は、結果が以下のADCRESULTレジスタに格納されます。

ADCINAO -> ADCRESULTO

ADCINBO -> ADCRESULT1

ADCINA1 -> ADCRESULT2

ADCINB1 -> ADCRESULT3

ADCINA2 -> ADCRESULT4

ADCINB2 -> ADCRESULT5

ADCINA3 -> ADCRESULT6

ADCINB3 -> ADCRESULT7

ADCINA4 -> ADCRESULT8

ADCINB4 -> ADCRESULT9

ADCINA5 -> ADCRESULT10

ADCINB5 -> ADCRESULT11

ADCINA6 -> ADCRESULT12

ADCINB6 -> ADCRESULT13

ADCINA7 -> ADCRESULT14

ADCINB7 -> ADCRESULT15

```

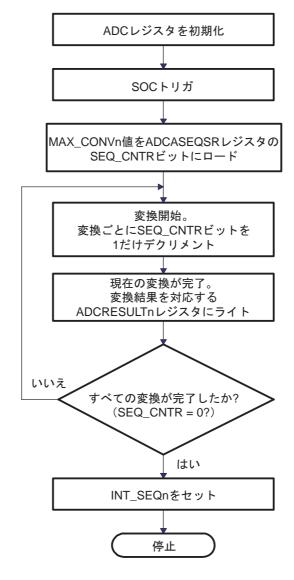

#### 1.3 割り込みなしのオートシーケンス・モード

以下の説明は 8 ステート・シーケンサに適用されます(SEQ1 または SEQ2)。このモードでは、SEQ1/SEQ2 が単一シーケンス・セッションで任意のチャネルの最大 8 変換までをオートシーケンスすることができます(シーケンサをカスケードにした場合は 16)。図 1-6 にフロー・チャートを示します。各変換の結果が 8 つのリザルト・レジスタのいずれかに格納されます(SEQ1 の場合は ADCRESULT0 ~ADCRESULT7、SEQ2 の場合は ADCRESULT8 ~ ADCRESULT15)。これらのレジスタは最下位アドレスから最上位アドレスに格納されます。

1 シーケンスの変換の数は MAX\_CONVn (ADCMAXCONV レジスタの 3 ビットまたは 4 ビット・フィールド)によって制御されます。オートシーケンス変換セッションの開始時に、これが自動的にオートシーケンス・ステータス・レジスタ(ADCASEQSR)のシーケンス・カウンタのステータス・ビット (SEQ\_CNTR[3:0]) にロードされます。MAX\_CONVn フィールドは  $0 \sim 7$  の値を格納できます(シーケンサをカスケードにした場合は  $0 \sim 15$ )。SEQ\_CNTR ビットはロードされた値からカウント・ダウンされます。これは、シーケンサがステート CONV00 から開始し、SEQ\_CNTR がゼロになるまで順番に続行される(CONV01、CONV02など) ためです。変換数はオートシーケンス・セッションが(MAX\_CONVn+1) のときに完了します。

# 例 1-3 SEQ1 を使用したデュアル・シーケンサ・モードの変換

SEQ1 から 7 つの変換を要求されたとします(ADCINA2 と ADCINA3 を 2 回入力、次に ADCINA6、ADCINA7、および ADCINB4 をオートシーケンス・セッションの一部として変換する)。次に、MAX CONV1 を 6 にセットし、ADCCHSELSEQn レジスタを表 1-3 に示す値にセットします。

シーケンサが変換開始(SOC)トリガを受信すると、変換が開始します。SOC トリガは SEQ\_CNTR ビットもロードします。ADCCHSELSEQn レジスタで指定されたチャネルが、事前に決定された順序で変換のために取得されます。各変換後に、SEQ\_CNTR ビットが自動的に 1 だけデクリメントされます。SEQ\_CNTR がゼロになると、ADCTRL1 レジスタの連続ラン・ビット(CONT\_RUN)のステータスに応じて 2 つの処理が実行されます。

図 1-6 のフロー・チャートを参照してください。

- CONT\_RUN がセットされている場合は、変換シーケンスが自動的に最初から再実行されます。つまり、SEQ\_CNTR に MAX\_CONV1 の初期値が再ロードされ、SEQ1 の状態が CONV00 にセットされます(その他のオプションについてはセクション 1.7 を参照)。この場合、データの上書きを避けるために、次の変換シーケンスが開始する前にリザルト・レジスタをリードしたことを確認する必要があります。ADC に組み込まれたアービトレーション・ロジックによって、コンテンションが発生してもリザルト・レジスタが破損することはありません。ADC モジュールのリード試行中に、ADC モジュールがリザルト・レジスタへのライトを試みます。

- CONT\_RUN がセットされていない場合は、シーケンサが最後の状態のままになり(この例では CONV06)、SEQ\_CNTR の値はゼロのままになります。次の SOC でシーケンスを繰り返すには、次の SOC の前に RST SEQn ビットを使用してシーケンサをリセットする必要があります。

SEQ\_CNTR がゼロになるたびに割り込みフラグがセットされる場合は(INT\_ENA\_SEQn = 1、INT\_MOD\_SEQn = 0)、割り込みサービス・ルーチン(ISR)で(必要に応じて)手動でシーケンサをリセットできます(ADCTRL2 レジスタの RST\_SEQn ビットを使用)。これによって SEQn の状態が元の値にリセットされます(SEQ1 の場合は CONV00、SEQ2 の場合は CONV08)。この機能はシーケンサを開始 / 停止する際に役立ちます。例 1-3 は表 1-2 に示す差異を除き、SEQ2 およびカスケード 16 ビット・シーケンサ(SEQ)にも適用されます。

| 表 1-3 | ADCCHS | ELSEQn | レジス | タの値 | (MAX_ | CONV1 | を6にセット | ) |

|-------|--------|--------|-----|-----|-------|-------|--------|---|

|       |        |        |     |     |       |       |        |   |

|       | ピット 15 ~ 12 <sup>(1)</sup> | ピット11 ~ 8 <sup>(1)</sup> | ピット7~4 <sup>(1)</sup> | ピット3~0 <sup>(1)</sup> |              |

|-------|----------------------------|--------------------------|-----------------------|-----------------------|--------------|

| 70A3h | 3                          | 2                        | 3                     | 2                     | ADCCHSELSEQ1 |

| 70A4h | Х                          | 12                       | 7                     | 6                     | ADCCHSELSEQ2 |

| 70A5h | Х                          | X                        | X                     | X                     | ADCCHSELSEQ3 |

| 70A6h | x                          | x                        | x                     | х                     | ADCCHSELSEQ4 |

(1) 値は 10 進数、x = 無視

#### 図 1-6 割り込みなしオートシーケンス・モードのフロー・チャート

A フロー・チャートは CONT\_RUN ビット = 0 および INT\_MOD\_SEQn ビット = 0 に対応します。

# 1.3.1 シーケンサの開始 / 停止モード (複数のタイム・シーケンス・トリガを使用するシーケンサの開始 / 停止動作)

割り込みなしのオートシーケンス・モードに加えて、任意のシーケンサ(SEQ1、SEQ2、または SEQ)を複数の変換開始(SOC)トリガに同期し、時間的に分割された停止/開始モードで動作させることができます。このモードは例 1-3 に似ていますが、最初のシーケンスの完了後に、シーケンサを初期状態 CONV00 にリセットすることなく、再トリガすることができます(割り込みサービス・ルーチンでシーケンサがリセットされない)。したがって、1 つの変換シーケンスが終了すると、シーケンサが現在の変換状態のままになります。このモードでは、ADCTRL1 レジスタの連続ラン・ビット(CONT\_RUN)をゼロ(ディスエーブル)に設定する必要があります。

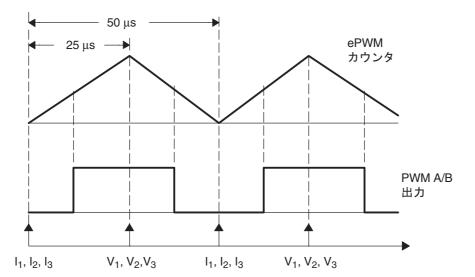

#### 例 1-4 シーケンサの開始 / 停止動作

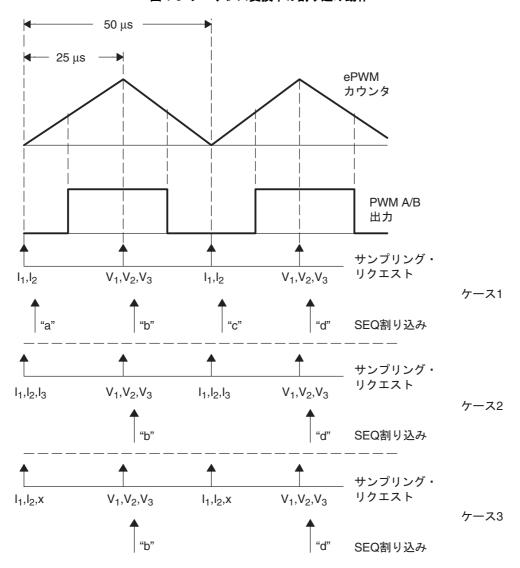

要件:3つの自動変換(たとえば、 $I_1,I_2,I_3$ )を開始するにはトリガ 1 (アンダーフロー)をオフにし、3 つの自動変換(たとえば、 $V_1,V_2,V_3$ )を開始するにはトリガ 2 (周期)をオフにします。トリガ 1 および 2 の時間間隔は 25 $\mu$ s で、ePWM によって提供されます。図 1-7 を参照してください。この場合は SEQ1 のみを使用します。

注: トリガ 1 および 2 は ePWM からの SOC 信号、外部ピン、またはソフトウェアの場合があります。この例のデュアル・トリガ要件を満たすために、同じトリガ・ソースが 2 回発生することがあります。複数の ePWM トリガが進行中のシーケンスによる原因で失われないように注意してください。セクション 1.3.3 を参照してください。

ここでは、MAX\_CONV1 が 2 にセットされ、ADC 入力チャネル選択シーケンス制御レジスタ (ADCCHSELSEQn) が表 1-4 に示すようにセットされます。

リセットされ初期化されると、SEQ1 がトリガを待ちます。最初のトリガによって、チャネル選択値が CONV00 ( $I_1$ )、CONV01 ( $I_2$ )、および CONV02 ( $I_3$ ) の 3 つの変換が実行されます。次に SEQ1 が現在の状態で次のトリガを待ちます。25 $\mu$ s 後の次のトリガにより、チャネル選択値が CONV03 ( $V_1$ )、CONV04 ( $V_2$ )、および CONV05 ( $V_3$ ) の別の 3 つの変換が発生します。

両方のトリガの場合に、MAX\_CONV1 の値が自動的に SEQ\_CNTR にロードされます。第2のトリガ・ポイントで異なる数の変換が必要な場合は、(第2のトリガより適切な時間だけ前に) ソフトウェアを使用して MAX\_CONV1 の値を変更する必要があります。それ以外の場合は、現在の値(最初にロードされた値)が再利用されます。これは、適切な時間に MAX\_CONV1 の値を変更する ISR によって実行できます。割り込み動作モードについてはセクション 1.3.4 を参照してください。

第2の自動変換セッションの終了時には、ADC リザルト・レジスタが表 1-5 に示す値になります。この時点で、SEQ1 は現在の状態で別のトリガを待ち続けます。ここで、ユーザーが(ソフトウェアで)SEQ1 を CONV00 の状態にリセットし、同じトリガ 1、2 のセッションを繰り返すことができます。

図 1-7 シーケンサを開始する ePWM トリガの例

| 表 1-4 | <b>ADCCHSELS</b> | EQn の値 | (MAX | CONV1 | を2にセ | ット) |

|-------|------------------|--------|------|-------|------|-----|

|-------|------------------|--------|------|-------|------|-----|

|       | ピット 15 ~ 12    | ビット11~8        | ビット7~4         | ピット3~0         |              |

|-------|----------------|----------------|----------------|----------------|--------------|

| 70A3h | V <sub>1</sub> | l <sub>3</sub> | l <sub>2</sub> | I <sub>1</sub> | ADCCHSELSEQ1 |

| 70A4h | X              | X              | $V_3$          | $V_2$          | ADCCHSELSEQ2 |

| 70A5h | X              | Х              | X              | x              | ADCCHSELSEQ3 |

| 70A6h | X              | X              | x              | X              | ADCCHSELSEQ4 |

表 1-5 第2の自動変換セッション後の値

| バッファ・レジスタ   | ADC 変換結果パッファ   |

|-------------|----------------|

| ADCRESULT0  | I <sub>1</sub> |

| ADCRESULT1  | $I_2$          |

| ADCRESULT2  | I <sub>3</sub> |

| ADCRESULT3  | $V_1$          |

| ADCRESULT4  | $V_2$          |

| ADCRESULT5  | $V_3$          |

| ADCRESULT6  | X              |

| ADCRESULT7  | X              |

| ADCRESULT8  | X              |

| ADCRESULT9  | X              |

| ADCRESULT10 | X              |

| ADCRESULT11 | x              |

| ADCRESULT12 | X              |

| ADCRESULT13 | X              |

| ADCRESULT14 | X              |

| ADCRESULT15 | X              |

#### 1.3.2 同時サンプリング・モード

1つの入力が ADCINA0 ~ ADCINA7 の範囲で、もう 1 つの入力が ADCINB0 ~ ADCINB7 の範囲の場合、 ADC は 2 つの ADCINxx 入力を同時にサンプリングすることができます。この場合 2 つの入力が同じサンプル・ホールド・オフセットを持つ必要があります(ADCINA7 と ADCINB6 ではなく ADCINA4 と ADCINB4)。 ADC を同時サンプリング・モードにするには、ADCTRL3 レジスタの SMODE\_SEL ビットをセットする必要があります。詳細については、セクション 1.2 を参照してください。

# 1.3.3 入力トリガの説明

各シーケンサにはイネーブル/ディスエーブルにすることができる複数のトリガ入力があります。SEQ1、 SEQ2、およびカスケード SEQ の有効な入力トリガについては、表 1-6 を参照してください。

表 1-6 入力トリガ

| SEQ1(シーケンサ 1)              | SEQ2(シーケンサ 2)              | カスケード SEQ                  |

|----------------------------|----------------------------|----------------------------|

| ソフトウェア・トリガ<br>(ソフトウェア SOC) | ソフトウェア・トリガ<br>(ソフトウェア SOC) | ソフトウェア・トリガ<br>(ソフトウェア SOC) |

| ePWMx SOCA<br>XINT2 ADCSOC | ePWMx SOCB                 | ePWMx SOCA<br>ePWMx SOCB   |

| , <u>_</u> ,               |                            | XINT2_ADCSOC               |

#### 注:

- シーケンサがアイドル状態のときは、いつでも SOC トリガによって自動変換シーケンスを開始できます。アイドル状態とは、トリガを受信する前の CONV00 の状態、または変換シーケンス完了時のシーケンサの状態 (SEQ CNTR のカウントがゼロになった状態) です。

- ・ 現在の変換シーケンスの進行中にSOCトリガが発生すると、ADCTRL2レジスタのSOC\_SEQN ビットがセットされます。このビットは前の変換シーケンスの開始時にクリアされているはず です。さらに別の SOCトリガが発生すると、これは失われます。つまり、SOC\_SEQn ビット がすでにセットされている場合(SOC 保留中)、後続のトリガは無視されます。

- ・ いったんトリガされると、シーケンス中にシーケンサを停止 / 一時停止することはできません。 プログラムがシーケンス終了 (EOS) まで待つか、シーケンサのリセットを開始する必要があ ります。リセットによってシーケンサが即座にアイドルの開始状態 (SEQ1 とカスケードの場 合は CONV00、SEQ2 の場合は CONV08) に戻ります。

- カスケード・モードで SEQ1/2 を使用する場合は、SEQ1 のトリガがアクティブな間は、SEQ2 に送信されるトリガは無視されます。カスケード・モードは8ステートではなく16ステートの SEQ1 だとみなすことができます。

#### 1.3.4 シーケンス変換中の割り込み動作

シーケンサは2つの動作モードにおいて割り込みを生成できます。モードはADCTRL2の割り込みモード・イネーブル制御ビットによって決定されます。

例 1-4 のバリエーションを使用して、さまざまな動作状態における割り込みモード 1 とモード 2 の使用 方法を示します。

ケース1:第1と第2シーケンスのサンプル数が等しくない

- モード1割り込み動作(すべての EOS で割り込みリクエストが発生)

- 1. MAX\_CONVn = 1 でシーケンサが初期化され、I<sub>1</sub> と I<sub>2</sub> を変換します。

- 2. ISR "a" で MAX\_CONVn が(ソフトウェアによって)2 に変更され、 $V_1$ 、 $V_2$ 、 $V_3$  を変換します。

- 3. ISR "b" で以下のイベントが発生します。

- a. MAX\_CONVn が再度 1 に変更され、I<sub>1</sub> と I<sub>2</sub> を変換します。

- b. 値  $I_1$ 、 $I_2$ 、 $V_1$ 、 $V_2$ 、 $V_3$  が ADC リザルト・レジスタからリードされます。

- c. シーケンサがリセットされます。

- 4. ステップ2と3を繰り返します。SEQ\_CNTRがゼロになるたびに割り込みフラグがセットされ、 両方の割り込みが認識されます。

#### ケース2:第1と第2シーケンスのサンプル数が等しい

- モード2割り込み動作(1つおきの EOS で割り込みリクエストが発生)

- 1.  $MAX\_CONVn = 2$  でシーケンサが初期化され、 $I_1$ 、 $I_2$ 、 $I_3$ (または  $V_1$ 、 $V_2$ 、 $V_3$ )を変換します。

- 2. ISR "b" と "d" で以下のイベントが発生します。

- a. 値  $I_1$ 、 $I_2$ 、 $I_3$ 、 $V_1$ 、 $V_2$ 、 $V_3$  が ADC リザルト・レジスタからリードされます。

- b. シーケンサがリセットされます。

- 3. ステップ2を繰り返します。

# **ケース3**: 第1と第2シーケンスのサンプル数が等しい(ダミー・リード実行)

- モード2割り込み動作(1つおきの EOS で割り込みリクエストが発生)

- 1.  $l_1$ 、 $l_2$ 、x(ダミー・サンプル)のために、MAX\_CONVn = 2 でシーケンサが初期化されます。

- 2. ISR "b" と "d" で以下のイベントが発生します。

- a. 値  $I_1$ 、 $I_2$ 、x、 $V_1$ 、 $V_2$ 、 $V_3$  が ADC リザルト・レジスタからリードされます。

- b. シーケンサがリセットされます。

3. ステップ 2 を繰り返します。第 3 の I サンプル (x) はダミー・サンプルで実際は必要ありません。 ただし、ISR のオーバーヘッドと CPU の介入を最小限にするために、モード 2 の 1 つおきの割り込みリクエストの利点を活かしています。

図 1-8 シーケンス変換中の割り込み動作

#### 1.4 ADC クロック・プリスケーラ

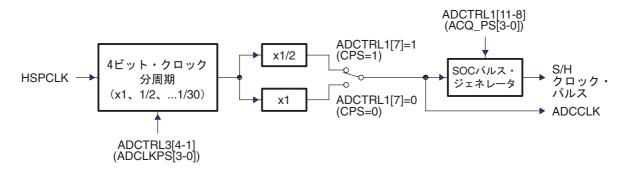

ペリフェラル・クロックHSPCLKは、ADCTRL3レジスタのADCCLKPS[3:0] ビットで分周されADCTRL1レジスタの CPS ビットによって追加で 2 分周が提供されます。さらに、サンプリング / 取得周期を長くして、電源インピーダンスの変動に対応するように ADC を調整できます。これは ADCTRL1レジスタの ACQ\_PS[3:0] ビットによって制御されます。これらのビットは S/H の変換部分と変換プロセスには影響しませんが、変換パルスの開始を延ばすことで、サンプリング部分の時間が長くなります。図 1-9を参照してください。

#### 図 1-9 ADC コア・クロックとサンプル・ホールド (S/H) クロック

A クロック分周期と S/H パルス制御についてはレジスタ・ビットの定義を参照してください。S/H パルス幅によって取得ウィンドウのサイズ(サンプリング・スイッチを閉じる時間)が決定します。

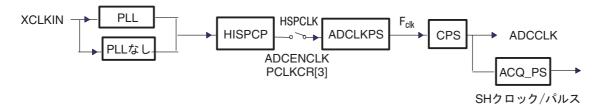

#### 1.4.1 ADC モジュールのクロックおよびサンプル・レート

ADC モジュールには複数のプリスケーラ・ステージがあり、必要な ADC の動作クロック速度が生成されます。以下の図は ADC モジュールに供給されるクロックの選択段階を示しています。

#### 図 1-10 ADC へのクロック・チェーン

表 1-7 ADC へのクロック・チェーン

| XCLKIN | PLLCR[3:0] | HISPCLK                         | ADCTRL3[4-1]              | ADCTRL1[7]                          | ADCCLK        | ADCTRL1[11-8]         | SH 幅 |

|--------|------------|---------------------------------|---------------------------|-------------------------------------|---------------|-----------------------|------|

| 20 MHz | 0000b      | HSPCP = 0                       | ADCLKPS = 0               | CPS=1                               |               | ACQ_PS = 0            |      |

|        | 10 MHz     | 10 MHz                          | 10 MHz                    | 5 MHz                               | 5 MHz         | SH パルス・<br>クロック       | 1    |

|        | 1010b      | HSPCP = 4                       | ADCLKPS = 2               | CPS = 1                             |               | ACQ_PS = 15           |      |

| 20 MHz | 100 MHz    | 100 MHz/<br>2 X 4 = 12.5<br>MHz | 12.5/2 X 2 =<br>3.125 MHz | 3.125 MHz/<br>2 X 1 = 1.5625<br>MHz | 1.5625<br>MHz | SH パルス /<br>クロック = 16 | 16   |

#### 1.5 低電力モード

ADCは、ADCTRL3レジスタの独立したビットによって制御される3つの個別の電力をサポートします。これら3つのビットを組み合わせて、ADC電源投入、ADC電源切断、ADCオフの3つの電力レベルを形成します。

| 表 1 | -8 | 雷ナ | 1オ 7 | プシ | = | ン |

|-----|----|----|------|----|---|---|

|     |    |    |      |    |   |   |

| 電力レベル    | ADCBGRFDN1 | ADCBGRFDN0 | ADCPWDN |

|----------|------------|------------|---------|

| ADC 電源投入 | 1          | 1          | 1       |

| ADC 電源切断 | 1          | 1          | 0       |

| ADC オフ   | 0          | 0          | 0       |

| 予約       | 1          | 0          | X       |

| 予約       | 0          | 1          | X       |

#### 1.6 電源投入シーケンス

ADC が ADC オフ状態にリセットされます。ADC の電源を投入する際には以下のシーケンスを使用します。

- 1. 外部リファレンスが必要な場合は、ADCREFSEL レジスタの  $15 \sim 14$  ビットを使用してこのモード をイネーブルにします。バンド・ギャップの電源を投入する前にこのモードをイネーブルにする必要があります。

- 2. ADCTRL3 レジスタのビット 7 ~ 5 (ADCBGRFDN[1:0]、ADCPWDN) をセットして、リファレンス、バンド・ギャップ、アナログ回路の電源を投入します。

- 3. 最初の変換を行う前に 5ms の遅延が必要です。

ADC の電源を切断する際は、3 つのビットすべてを同時にクリアできます。ADC の電力レベルはソフトウェアによって制御され、デバイスの電力モード状態とは独立している必要があります。

場合によっては、ADCPWDN ビットのみをクリアして、バンド・ギャップとリファレンスに電源投入したまま、ADC の電源を切断するほうが望ましいこともあります。ADC に再度電源を投入する際は、このビットをセットしてから変換を実行するまでに 20μs の遅延が必要です。

注: F280x ADC の場合は、すべての回路の電源を投入してから 5ms の遅延が必要です。この点が F281x ADC と異なります。

#### 1.7 シーケンサ・オーバーライド機能

通常の動作では、シーケンサ SEQ1、SEQ2 またはカスケード SEQ1 が、選択した ADC チャネルの変換に役立ち、これらを対応する ADCRESULTn レジスタに順次格納します。シーケンサは MAX\_CONVn セットの最後で最初に戻ります。シーケンサ・オーバーライド機能により、シーケンサの循環をソフトウェアによって制御できます。シーケンサ・オーバーライド機能は、ADC 制御レジスタ 1 (ADCCTRL1) のビット 5 によって制御されます。

たとえば、SEQ\_OVRD ビットが 0 で、ADC がカスケード・シーケンサ内で、MAX\_CONV1 が 7 にセットされた連続変換モードであるとします。通常は、ADC 変換とともにシーケンサが順次インクリメントされ、ADCRESULT7 レジスタまで更新されて 0 に戻ります。ADCRESULT7 レジスタ更新の最後で、関連する割り込みフラグがセットされます。

SEQ\_OVRD ビットを 1 にセットすると、シーケンサが 7 つのリザルト・レジスタを更新しますが、0 には戻りません。この場合は、シーケンサが順次インクリメントされ、ADCRESULT8 レジスタを更新し、ADCRESULT15 レジスタに達するまで続行します。ADCRESULT15 レジスタを更新すると 0 に戻ります。この機能はリザルト・レジスタ(0 ~ 15)を FIFO のように扱い、ADC からの順次データ・キャプチャが行われます。ADC 変換を最大データ転送速度で行う場合に、ADC データをキャプチャするためにこの機能が非常に役立ちます。

シーケンサ・オーバーライド機能の推奨事項と注意事項を以下に示します。

- リセット後は SEQ\_OVRD ビットが 0 になるため、シーケンサ・オーバーライド機能はディスエーブルのままです。

- SEQ\_OVRD ビットを MAX\_CONVn のゼロ以外のすべての値にセットすると、関連する割り込みフラグ・ビットが、リザルト・レジスタ更新の MAX\_CONVn カウントごとにセットされます。

- たとえば、ADCMAXCONVを3にセットすると、4つのリザルト・レジスタ更新ごとに選択されたシーケンサの割り込みフラグがセットされます。シーケンサの最後で必ず最初に戻ります(カスケード・シーケンサ・モードでは ADCRESULT15 レジスタの更新後)。

- これは SEQ1、SEQ2、および SEQ1 を使用するカスケード・シーケンサによる変換で機能します。

- この機能をプログラム内で動的にイネーブルにしたり、制御することは避けてください。この機能 は必ず ADC モジュール初期化中にイネーブルにする必要があります。

- 連続変換モードでシーケンサが変更されると、ADC チャネル・アドレスは CONVxx レジスタの事前 にセットされた値を使用します。同じチャネルの連続変換が必要な場合は、すべての CONVxx レジ スタが同じチャネル・アドレスを持つ必要があります。

- 連続変換モードでシーケンサのリセットが必要な場合は、CONT\_RUN ビットを 0 にセットし、ADC クロック・ドメインで 2 サイクル待ち、それからシーケンサをリセットします。これで、CONT\_RUN を再度 1 にセットすることができます。

- たとえば、シーケンサ・オーバーライド機能を使用して、ADCINAO チャネルの 16 の連続サンプルを取得するには、16 すべての CONVxx レジスタを 0x0000 にセットする必要があります。

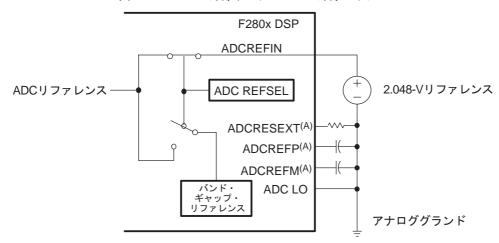

#### 1.8 内部 / 外部リファレンス電圧の選択

デフォルトでは、内部で発生したバンド・ギャップ電圧リファレンスが選択され、ADC ロジックが供給されます。

お客様のアプリケーション要件に基づいて、ADC ロジックが外部電圧リファレンスによって供給される 場合もあります。280x ADC は、ADCREFIN ピンで 2.048V、1.5V、または 1.024V を受け付けます。 ADCREFSEL レジスタの値によって、選択されるリファレンス・ソースが決定されます。

内部リファレンス・オプションを選択すると、ADCREFIN ピンを選択したソースに接続したままにする、接続しない、または接地することができます。いずれのオプションを選択した場合でも、ADCRESEXT、ADCREFP、およびADCREFMピンの外部回路は同じです。

2.048Vの外部リファレンス電圧は、業界標準リファレンス・コンポーネントに合わせて選択されました。これらのコンポーネントにはさまざまな温度定格のものがあります。推奨する TI の部品は REF3020AIDBZ です。

図 1-11 2.048-V 外部リファレンスの外部パイアス

A コンポーネント値については、『TMS320F2808, TMS320F2806, TMS320F2801, UCD9501 Digital Signal Processors Data Manual』(文書番号 SPRS230)を参照してください。

#### 1.9 オフセット誤り訂正

280x ADC は ADC オフセット・トリム・レジスタ(ADCOFFTRIM)の 9 ビット・フィールドによるオフセット訂正をサポートします。

ADC リザルト・レジスタに結果を格納する前に、このレジスタに格納された値が加算/減算されます。この演算は ADC モジュールに含まれるため、結果のタイミングは影響を受けません。

さらに、演算が ADC 内部で処理されるため、調整された値に対して ADC のフル・ダイナミック・レンジが保持されます。

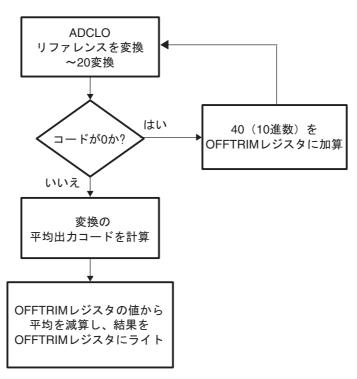

このレジスタの適切な値を見つけるには、ADCLO をいずれかの ADC チャネルに接続し、中心のゼロ・コードが見えるまで、さまざまなレジスタ値を使用してこのチャネルを変換します。図 1-12 のフロー・チャートを参照してください。

図 1-12 オフセット誤り訂正プロセスのフロー・チャート

# 例1-5 負のオフセット

開始時には、ほとんどのリファレンス変換の結果がゼロになります。値 0x28 (10 進数の 40) を OFFTRIM レジスタにライトすると、すべてのリファレンス変換の結果が正になり、平均が 0x19 (10 進数の 25) になります。OFFTRIM レジスタにライトされる最終的な値は 0x0F (10 進数の 15) に なります。

#### 例1-6 正のオフセット

開始時には、すべてのリファレンス変換の結果が正になり、平均が 0x14 (10 進数の 20) になります。OFFTRIM レジスタにライトされる最終的な値は 0x1EC (10 進数の -20) になります。

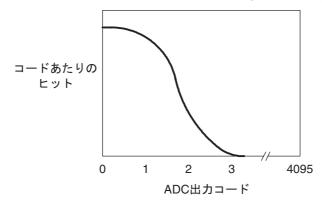

オフセット誤り訂正プロセスが完了し、複数の ADCLO サンプルが変換されると、図 1-13 のように半分の鐘形曲線になります。コンバータはゼロのコードで最低値に達するため、鐘形曲線の半分は表示されません。

# 図 1-13 サンプリングされた 0-V リファレンスの最適なコード分布

# ADC レジスタ

この章では ADC レジスタとビットの定義について取り上げます。レジスタは機能別にまとめら れています。

| 項目  |                                | ページ |

|-----|--------------------------------|-----|

| 0.4 |                                |     |

| 2.1 | ADC 制御レジスタ                     | 36  |

| 2.2 | 最大変換チャネル・レジスタ(ADCMAXCONV)      | 40  |

| 2.3 | オートシーケンス・ステータス・レジスタ(ADCASEQSR) | 42  |

| 2.4 | ADC ステータス・フラグ・レジスタ(ADCST)      | 43  |

| 2.5 | ADC リファレンス選択レジスタ(ADCREFSEL)    | 44  |

| 2.6 | ADC オフセット・トリム・レジスタ(ADCOFFTRIM) | 44  |

| 2.7 | ADC 入力チャネル選択シーケンス制御レジスタ        | 44  |

| 2.8 | ADC 変換結果パッファ・レジスタ(ADCRESULTn)  | 45  |

|     |                                |     |

# 2.1 ADC 制御レジスタ

# 図 2-1 ADC 制御レジスタ 1 (ADCTRL1) (アドレス・オフセット 00h)

| <br>15 | 14       | 13       | 12       | 11 |        | 8 |

|--------|----------|----------|----------|----|--------|---|

| 予約     | RESET    | SUSMOD   |          |    | ACQ_PS |   |

| R-0    | R/W-0    | R/V      | V-0      |    | R/W-0  |   |

| <br>7  | 6        | 5        | 4        | 3  |        | 0 |

| CPS    | CONT_RUN | SEQ_OVRD | SEQ_CASC |    | 予約     |   |

|        |          |          |          |    |        |   |

凡例:R/W=リード/ライト、R=リードのみ、-n=リセット後の値

#### 表 2-1 ADC 制御レジスタ 1 (ADCTRL1) のフィールドの説明

| ビット   | 名前          | 値  | 説明                                                                                                                                                                                                                                                                                                               |

|-------|-------------|----|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 15    | 予約          |    | リードしてゼロを返します。ライトしても何の影響もありません。                                                                                                                                                                                                                                                                                   |

| 14    | RESET       |    | ADC モジュール・ソフトウェアのリセット。このビットによって ADC モジュール全体のマスタ・リセットを行います。<br>すべてのレジスタ・ビットとシーケンサ・ステート・マシンが、デバイス・リセット・ピンが Low にされたとき(またはパワー・オン・リセット後)の初期状態にリセットされます。これは1回限り効果があるビットで、1にセットされるとビット自体が即座にクリアされます。このビットのリードは常に0を返します。また、ADCのリセットには2クロック・サイクルの遅延があります。つまり、ADC リセットの命令後、ADCの2クロック・サイクルが過ぎるまでは他のADC 制御レジスタ・ビットを変更できません。 |

|       |             | 0  | 影響なし。                                                                                                                                                                                                                                                                                                            |

|       |             | 1  | ADC モジュール全体をリセットします(ADC ロジックによってビットが 0 にセットされる)。                                                                                                                                                                                                                                                                 |

|       |             |    | 注: ADC モジュールはシステム・リセット中にリセットされます。それ以外のときに ADC モジュールをリセットする必要がある場合は、このビットに 1 をライトすれば可能です。ADC クロック・ドメインの 2 サイクル後に、ADCCTRL1 レジスタ・ビットに適切な値をライトできます。以下の例は 100-MHz DSP クロックと 12.5-MHz ADCCLK の場合です。アセンブリ・コードを以下に示します。MOV ADCTRL1, #01xxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxx                                              |

| 13-12 | SUSMOD[1:0] |    | エミュレーションの一時停止モード。これらのビットは、エミュレーションの一時停止 (たとえば、デバッガがブレークポイントを検出したため)が発生したときの動作を決定します。                                                                                                                                                                                                                             |

|       |             | 00 | モード 0。エミュレーションの一時停止は無視されます。                                                                                                                                                                                                                                                                                      |

|       |             | 01 | モード 1。現在の <b>シーケンス</b> が完了し、最終結果がラッチされ、ステート・マシンが<br>更新された後で、シーケンサと他のラッパー・ロジックが停止します。                                                                                                                                                                                                                             |

|       |             | 10 | モード 2。現在の <b>変換</b> が完了し、結果がラッチされ、ステート・マシンが更新された後で、シーケンサと他のラッパー・ロジックが停止します。                                                                                                                                                                                                                                      |

|       |             | 11 | モード 3。エミュレーションが一時停止すると、即座にシーケンサと他のラッパー・ロジックが停止します。                                                                                                                                                                                                                                                               |

| 11-8  | ACQ_PS[3:0] |    | 取得ウィンドウのサイズ。このビット・フィールドが SOC パルス幅を制御し、この パルス幅がサンプリング・スイッチを閉じる時間を決定します。SOC パルス幅は ADCTRL1[11:8] + 1 × ADCLK 周期です。                                                                                                                                                                                                  |

| 7     | CPS         |    | コア・クロック・プリスケーラ。プリスケーラは分周されたデバイス・ペリフェラル・クロック HSPCLK に適用されます。                                                                                                                                                                                                                                                      |

|       |             | 0  | ADCCLK = F <sub>clk</sub> /1                                                                                                                                                                                                                                                                                     |

|       |             | 1  | ADCCLK = F <sub>Clk</sub> /2                                                                                                                                                                                                                                                                                     |

|       |             |    | 注:F <sub>clk</sub> = 分周された HSPCLK (ADCCLKPS[3:0])                                                                                                                                                                                                                                                                |

# 表 2-1 ADC 制御レジスタ 1 (ADCTRL1) のフィールドの説明 (続き)

| ビット | 名前       | 値 | 説明                                                                                                                                                                                                                                                                               |

|-----|----------|---|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 6   | CONT_RUN |   | 連続ラン。このビットが、シーケンサが連続変換モードで動作するか、開始 / 停止モードで動作するかを決定します。このビットは、現在の変換シーケンスがアクティブな間にライトすることができます。このビットは、現在の変換シーケンスの終了時に有効になります。つまり、EOS が発生するまでは、有効なアクションを実行するためにソフトウェアでこのビットをセット / クリアすることができます。連続変換モードではシーケンサをリセットする必要はありませんが、開始 / 停止モードではシーケンサをリセットしてコンバータを CONVOO の状態にする必要があります。 |

|     |          | 0 | 開始 / 停止モード。EOS に達するとシーケンサが停止します。シーケンサをリセットしない場合は、シーケンサが終了したときの状態で次の SOC からシーケンサが開始します。                                                                                                                                                                                           |

|     |          | 1 | 連続変換モード。EOS に達したときのシーケンサの動作は、SEQ_OVRD ビットの状態によって異なります。このビットがクリアされた場合は、シーケンサがリセット状態から再開します(SEQ1とカスケードの場合はCONV00、SEQ2の場合はCONV08)。SEQ_OVRD がセットされた場合は、シーケンサがリセットなしで現在の位置から再開始します。                                                                                                   |

| 5   | SEQ_OVRD |   | シーケンサ・オーバーライド。MAX_CONVn によってセットされた変換終了時に 0 に戻るのを無効にして、連続ラン・モードでのシーケンサの柔軟性を高めます。                                                                                                                                                                                                  |

|     |          | 0 | ディスエーブル-MAX_CONVnによってセットされた変換終了時にシーケンサが0に戻ります。                                                                                                                                                                                                                                   |

|     |          | 1 | イネーブル - MAX_CONVn によってセットされた変換終了時にシーケンサは 0 に戻りません。シーケンサの終了時にのみ 0 に戻ります。                                                                                                                                                                                                          |

| 4   | SEQ_CASC |   | カスケード・シーケンサ動作。このビットは、SEQ1 と SEQ2 が 2 つの 8 ステート・シーケンサとして動作するか、1 つの 16 ステート・シーケンサ (SEQ) として動作するかを決定します。                                                                                                                                                                            |

|     |          | 0 | デュアル・シーケンサ・モード。SEQ1 と SEQ2 が 2 つの 8 ステート・シーケンサとして動作します。                                                                                                                                                                                                                          |

|     |          | 1 | カスケード・モード。SEQ1 と SEQ2 が 1 つの 16 ステート・シーケンサ(SEQ)として動作します。                                                                                                                                                                                                                         |

| 3-0 | 予約       |   | リードしてゼロを返します。ライトしても何の影響もありません。                                                                                                                                                                                                                                                   |

# 図 2-2 ADC 制御レジスタ 2(ADCTRL2)(アドレス・オフセット 01h)

| 15            | 14       | 13       | 12  | 11           | 10           | 9   | 8              |

|---------------|----------|----------|-----|--------------|--------------|-----|----------------|

| ePWM_SOCB_SEQ | RST_SEQ1 | SOC_SEQ1 | 予約  | INT_ENA_SEQ1 | INT_MOD_SEQ1 | 予約  | ePWM_SOCA_SEQ1 |

| R/W-0         | R/W-0    | R/W-0    | R-0 | R/W-0        | R/W-0        | R-0 | R/W-0          |

| 7             | 6        | 5        | 4   | 3            | 2            | 1   | 0              |

| EXT_SOC_SEQ1  | RST_SEQ2 | SOC_SEQ2 | 予約  | INT_ENA_SEQ2 | INT_MOD_SEQ2 | 予約  | ePWM_SOCB_SEQ2 |

| R/W-0         | R/W-0    | R/W-0    | R-0 | R/W-0        | R/W-0        | R-0 | R/W-0          |

凡例:R/W = リード / ライト、R = リードのみ、W = ライト・アクセス、S = セットのみ、C = クリア、-n = リセット後の値

#### 表 2-2 ADC 制御レジスタ 2 (ADCTRL2) のフィールドの説明

| ビット | 名前            | 値 | 説明                                                                                                                                                                                                                |

|-----|---------------|---|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 15  | ePWM_SOCB_SEQ |   | カスケード・シーケンサの場合に ePWM SOCB イネーブル( <i>注:このビットはカス</i><br>ケード・モードでのみアクティブ)。                                                                                                                                           |

|     |               | 0 | アクションなし。                                                                                                                                                                                                          |

|     |               | 1 | このビットをセットすると、カスケード・シーケンサを ePWM SOCB 信号によって開始できます。<br>さまざまなイベントによって変換を開始するように ePWM モジュールをプログラムできます。ePWM モジュールの詳細については、『TMS320x280x Enhanced Pulse Width Modulation Module Reference Guide』(文書番号 SPRU791)を参照してください。 |

| 14  | RST_SEQ1      |   | シーケンサ 1 をリセット。このビットに 1 をライトすると、SEQ1 またはカスケード・シーケンサが即座にプリトリガされた初期状態にリセットされます。つまり、CONV00 でトリガを待ちます。現在アクティブな変換シーケンスは中止されます。                                                                                          |

|     |               | 0 | アクションなし。                                                                                                                                                                                                          |

|     |               | 1 | シーケンサを CONV00 の状態に即座にリセットします。                                                                                                                                                                                     |

# 表 2-2 ADC 制御レジスタ 2(ADCTRL2)のフィールドの説明(続き)

| ビット | 名前             | 値 | 説明                                                                                             |

|-----|----------------|---|------------------------------------------------------------------------------------------------|

|     | SOC_SEQ1       |   | シーケンサ 1(SEQ1)またはカスケード・シーケンサの変換開始(SOC)トリガ。                                                      |

|     |                |   | このビットは以下のトリガによってセットできます。                                                                       |

|     |                |   | ・ S/W - ソフトウェアがこのビットに 1 をライト                                                                   |

|     |                |   | • ePWM SOCA                                                                                    |

|     |                |   | ・ ePWM SOCB(カスケード・モードのみ)                                                                       |

|     |                |   | • EXT - 外部ピン。つまり、GPIOxINT2SEL レジスタで XINT2 として設定された GPIO ポート A ピン(GPIO31-0)                     |

|     |                |   | GPIO ホートAEフ(GPIO31-0)<br>  GPIO ピンを XINT2 として設定する方法については、 <i>『TM</i> S320x280x System Control  |

|     |                |   | and Interrupts Reference Guide』(文書番号 SPRU712)を参照してください。トリガが発生したときに、以下の3つのケースが起こる可能性があります。      |

|     |                |   | <b>ケース 1</b> : SEQ1 アイドル、SOC ビットはクリア。SEQ1 が即座に開始します(アービタの制御下)。                                 |

|     |                |   | このビットをセットおよびクリアして、保留中のトリガ・リクエストを受け付けます。<br>ケース 2: SEQ1 ビジー、SOC ビットはクリア。ビットがセットされ、トリガ・リク        |

|     |                |   | エストが保留中であることを示します。<br>現在の変換終了後に SEQ1 が開始すると、このビットがクリアされます。                                     |

|     |                |   | <b>ケース 3</b> : SEQ1 ビジー、SOC ビットはセット。この場合、発生したトリガは無視されます(ロスト)。                                  |

|     |                | 0 | 保留中の SOC トリガをクリアします。                                                                           |

|     |                |   | 注:シーケンサがすでに開始している場合は、このビットが自動的にクリアされるため、ゼロをライトしても影響はありません。このビットをクリアしても、すでに開始したシーケンサは停止できません。   |

|     |                | 1 | ソフトウェア・トリガ - 現在停止している位置から SEQ1 を開始します(アイドル・モード)。                                               |

|     |                |   | 注:RST_SEQ1(ADCTRL2.14)および SOC_SEQ1(ADCTRL2.13)ビットを同じ                                           |

|     |                |   | 命令内でセットすることはできません。これによってシーケンサがリセットされます                                                         |

|     |                |   | が、シーケンスは開始されません。正しい順序は、まず RST_SEQ1 ビットをセット<br>してから、次の命令内で SOC_SEQ1 ビットをセットします。これによって確実に        |

|     |                |   | してから、次の叩っ内で SOC_SEQT ビットをセットします。これによって確実に<br> シーケンサがリセットされ、新規シーケンスが開始します。この順序は RST_SEQ2        |

|     |                |   | (ADCTRL2.6) および SOC_SEQ2 (ADCTRL2.5) ビットにも適用されます。                                              |

| 12  | 予約             |   | リードしてゼロを返します。ライトしても何の影響もありません。                                                                 |

| 11  | INT_ENA_SEQ1   |   | SEQ1 割り込みイネーブル。このビットが INT SEQ1 による CPU 割り込みリクエストをイネーブルにします。                                    |

|     |                | 0 | INT_SEQ1 による割り込みリクエストをディスエーブルにします。                                                             |

|     |                | 1 | INT_SEQ1 による割り込みリクエストをイネーブルにします。                                                               |

| 10  | INT_MOD_SEQ1   |   | SEQ1 割り込みモード。このビットが SEQ1 割り込みモードを選択します。これは、<br>SEQ1 の変換シーケンス終了時の INT SEQ1 のセットに影響します。          |

| Į.  |                | 0 | INT_SEQ1 が SEQ1 シーケンスの終了ごとにセットされます。                                                            |

|     |                | 1 | INT_SEQ1 が SEQ1 シーケンスの終了 1 回おきにセットされます。                                                        |

| 9   | 予約             |   | リードしてゼロを返します。ライトしても何の影響もありません。                                                                 |

| 8   | ePWM_SOCA_SEQ1 |   | SEQ1 の ePWM SOCA イネーブル・ビット。                                                                    |

|     |                | 0 | SEQ1 を ePWMx SOCA トリガで開始できません。                                                                 |

|     |                | 1 | SEQ1/SEQ を ePWMx SOCA トリガで開始できます。さまざまなイベントによって<br>変換を開始するように ePWM をプログラムできます。                  |

| 7   | EXT_SOC_SEQ1   |   | SEQ1 の外部信号変換開始ビット。                                                                             |

|     |                | 0 | アクションなし。                                                                                       |

|     |                | 1 | このビットをセットすると、GPIOXINT2SEL レジスタで XINT2 として設定された GPIO ポート A ピン(GPIO31-0)からの信号で、ADC 自動変換シーケンスを開始で |

|     |                |   | きます。『TMS320x280x System Control and Interrupts Reference Guide』(SPRU712)<br>を参照してください。         |

| 6   | RST_SEQ2       |   | SEQ2 をリセット。                                                                                    |

|     |                | 0 | アクションなし。                                                                                       |

|     |                | 1 | SEQ2 を即座にプリトリガされた初期状態にリセットします。つまり、CONV08 でトリガを待ちます。現在アクティブな変換シーケンスは中止されます。                     |

# 表 2-2 ADC 制御レジスタ 2 (ADCTRL2) のフィールドの説明 (続き)

| ビット | 名前             | 値 | 説明                                                                                                                                                                                                                                                                                                                                                                                                                   |

|-----|----------------|---|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 5   | SOC_SEQ2       |   | シーケンサ 2 (SEQ2) の変換開始トリガ (デュアル・シーケンサ・モードにのみ適用、カスケード・モードでは無視)。このビットは以下のトリガによってセットできます。 ・ S/W - ソフトウェアがこのビットに 1 をライト ・ ePWM SOCB トリガが発生したときに、以下の 3 つのケースが起こる可能性があります。 ケース 1: SEQ2 アイドル、SOC ビットはクリア。SEQ2 が即座に開始します(アービタの制御下)。ビットがクリアされると、保留中のトリガ・リクエストを受け付けます。 ケース 2: SEQ2 ビジー、SOC ビットはクリア。ビットがセットされ、トリガ・リクエストが保留中であることを示します。 現在の変換終了後に SEQ2 が開始すると、このビットがクリアされます。 ケース 3: SEQ2 ビジー、SOC ビットはセット。この場合、発生したトリガは無視されます(ロスト)。 |

|     |                | 0 | 保留中の SOC トリガをクリアします。<br>注:シーケンサがすでに開始している場合は、このビットが自動的にクリアされるため、ゼロをライトしても影響はありません。このビットをクリアしても、すでに開始したシーケンサは停止できません。                                                                                                                                                                                                                                                                                                 |

|     |                | 1 | 現在停止している位置から SEQ2 を開始します(アイドル・モード)。                                                                                                                                                                                                                                                                                                                                                                                  |

| 4   | 予約             |   | リードしてゼロを返します。ライトしても何の影響もありません。                                                                                                                                                                                                                                                                                                                                                                                       |

| 3   | INT_ENA_SEQ2   |   | SEQ2 割り込みイネーブル。このビットが、INT SEQ2 による CPU への割り込みリクエストをイネーブルまたはディスエーブルにします。                                                                                                                                                                                                                                                                                                                                              |

|     |                | 0 | INT_SEQ2 による割り込みリクエストをディスエーブルにします。                                                                                                                                                                                                                                                                                                                                                                                   |

|     |                | 1 | INT_SEQ2 による割り込みリクエストをイネーブルにします。                                                                                                                                                                                                                                                                                                                                                                                     |

| 2   | INT_MOD_SEQ2   |   | SEQ2 割り込みモード。このビットが SEQ2 割り込みモードを選択します。これは、<br>SEQ2 の変換シーケンス終了時の INT SEQ2 のセットに影響します。                                                                                                                                                                                                                                                                                                                                |

|     |                | 0 | INT_SEQ2 が SEQ2 シーケンスの終了ごとにセットされます。                                                                                                                                                                                                                                                                                                                                                                                  |

|     |                | 1 | INT_SEQ2 が SEQ2 シーケンスの終了1回おきにセットされます。                                                                                                                                                                                                                                                                                                                                                                                |

| 1   | 予約             |   | リードしてゼロを返します。ライトしても何の影響もありません。                                                                                                                                                                                                                                                                                                                                                                                       |

| 0   | ePWM_SOCB_SEQ2 |   | SEQ2 の ePWM SOCB イネーブル・ビット。                                                                                                                                                                                                                                                                                                                                                                                          |

|     |                | 0 | SEQ2 を ePWMx SOCA トリガで開始できません。                                                                                                                                                                                                                                                                                                                                                                                       |

|     |                | 1 | SEQ2 を ePWMx SOCA トリガで開始できます。 さまざまなイベントによって変換を<br>開始するように ePWM をプログラムできます。                                                                                                                                                                                                                                                                                                                                           |

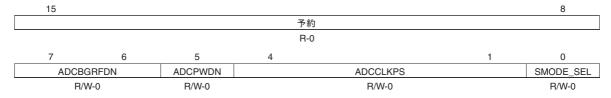

# 図 2-3 ADC 制御レジスタ 3 (ADCTRL3) (アドレス・オフセット 18h)

凡例: R/W = リード / ライト、R = リードのみ、-n = リセット後の値

# 表 2-3 ADC 制御レジスタ 3 (ADCTRL3) のフィールドの説明

| ビット  | 名前             | 値  | 説明                                                                                                                   |

|------|----------------|----|----------------------------------------------------------------------------------------------------------------------|

| 15-8 | 予約             |    | リードしてゼロを返します。ライトしても何の影響もありません。                                                                                       |

| 7-6  | ADCBGRFDN[1:0] |    | ADC バンド・ギャップおよびリファレンスの電源切断。これらのビットがアナログ・コア内のバンド・ギャップとリファレンス回路の電源投入と電源切断を制御します。電源投入シーケンスの要件については、セクション 1.6 を参照してください。 |

|      |                | 00 | バンド・ギャップとリファレンス回路の電源が切断されます。                                                                                         |

|      |                | 11 | バンド・ギャップとリファレンス回路の電源が投入されます。                                                                                         |

# 表 2-3 ADC 制御レジスタ 3(ADCTRL3)のフィールドの説明(続き)

| ビット | 名前             | 値    | 説明                                                                                                                                                                         |

|-----|----------------|------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 5   | ADCPWDN        |      | ADC 電源切断。このビットが、バンド・ギャップとリファレンス回路を除く、アナログ・コア内のすべてのアナログ回路の電源投入と電源切断を制御します。電源投入シーケンスの要件については、セクション 1.6 を参照してください。                                                            |

|     |                | 0    | バンド・ギャップとリファレンス回路を除く、コア内のすべてのアナログ回路の電源<br>が切断されます。                                                                                                                         |

|     |                | 1    | コア内のアナログ回路の電源が投入されます。                                                                                                                                                      |

| 4-1 | ADCCLKPS [3:0] |      | コア・クロック分周器。28x ペリフェラル・クロック、HSPCLK が 2*ADCCLKPS[3-0] によって分周されます。ただし、ADCCLKPS[3-0] が 0000 の場合は例外で、HSPCLK が直接渡されます。分周されたクロックはさらに ADCTRL1[7]+1 によって分周され、コア・クロック ADCLK が生成されます。 |

|     |                |      | ADCCLKPS [3:0] コア・クロック分周器 ADCLK                                                                                                                                            |

|     |                | 0000 | 0 HSPCLK/(ADCTRL1[7] + 1)                                                                                                                                                  |

|     |                | 0001 | 1 HSPCLK/[2*(ADCTRL1[7] + 1)]                                                                                                                                              |

|     |                | 0010 | 2 HSPCLK/[4*(ADCTRL1[7] + 1)]                                                                                                                                              |

|     |                | 0011 | 3 HSPCLK/[6*(ADCTRL1[7] + 1)]                                                                                                                                              |

|     |                |      | 4 HSPCLK/[8*(ADCTRL1[7] + 1)]                                                                                                                                              |

|     |                |      | 5 HSPCLK/[10*(ADCTRL1[7] + 1)]                                                                                                                                             |

|     |                |      | 6 HSPCLK/[12*(ADCTRL1[7] + 1)]                                                                                                                                             |

|     |                |      | 7 HSPCLK/[14*(ADCTRL1[7] + 1)]                                                                                                                                             |

|     |                |      | 8 HSPCLK/[16*(ADCTRL1[7] + 1)]                                                                                                                                             |

|     |                |      | 9 HSPCLK/[18*(ADCTRL1[7] + 1)]                                                                                                                                             |

|     |                |      | 10 HSPCLK/[20*(ADCTRL1[7] + 1)]                                                                                                                                            |

|     |                | 1011 |                                                                                                                                                                            |

|     |                | 1100 | 12 HSPCLK/[24*(ADCTRL1[7] + 1)]                                                                                                                                            |

|     |                | 1110 |                                                                                                                                                                            |

|     |                |      | 15 HSPCLK/[30*(ADCTRL1[7] + 1)]                                                                                                                                            |

| 0   | SMODE_SEL      | 1111 | サンプリング・モード選択。このビットが連続または同時サンプリング・モードを選                                                                                                                                     |

|     |                |      | 択します。                                                                                                                                                                      |

|     |                | 0    | 連続サンプリング・モードを選択します。                                                                                                                                                        |

|     |                | 1    | 同時サンプリング・モードを選択します。                                                                                                                                                        |

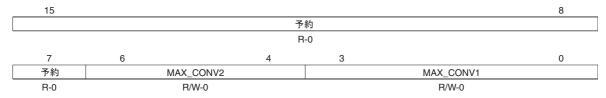

#### 2.2 最大変換チャネル・レジスタ (ADCMAXCONV)

# 図 2-4 最大変換チャネル・レジスタ(ADCMAXCONV)(オフセット・アドレス 02h)

凡例: R/W = リード / ライト、R = リードのみ、x = 不定、-n = リセット後の値

| ビット  | 名前        | 説明                                                                                                                                                                                                                                                                                                                                   |

|------|-----------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|