LM27762

JAJSCI0B - AUGUST 2016-REVISED FEBRUARY 2017

# LM27762 低ノイズ、正負電圧出力 チャージ・ポンプ、LDO内蔵

# 特長

- 可変の正電源電圧(1.5V~5V)と負電源電圧(-1.5V~-5V)を低ノイズで生成

- 入力電圧範囲: 2.7V~5.5V

- ±250mAの出力電流

- 反転チャージ・ポンプに続く負のLDO

- 2MHzの低ノイズ固定周波数動作

- $2.5\Omega$ のインバータ出力インピーダンス、 $V_{IN} = 5V$

- 負のLDOドロップアウト電圧: 100mAで30mV、  $V_{OUT} = -5V$

- 正のLDOドロップアウト電圧: 100mAで45mV、  $V_{OUT} = 5V$

- 静止電流: 390µA (標準値)

- シャットダウン時消費電流: 0.5µA (標準値)

- 電流制限と過熱保護

- パワー・グッド・ピン(アクティブLOW)

- WEBENCH® Power Designerにより、LM27762 を使用するカスタム設計を作成

# 2 アプリケーション

- Hi-Fiオーディオ・ヘッドフォン用アンプ

- オペアンプの雷力バイアス

- データ・コンバータの電源供給

- ワイヤレス通信システム

- インターフェイス電源

- ハンドヘルド計測機器

# 3 概要

LM27762は、±1.5V~±5Vの範囲で調整可能な非常に低 ノイズの正および負の出力電圧を供給できます。入力電 圧範囲は2.7V~5.5Vで、出力電流は最大±250mAです。 動作電流がわずか390µAで、シャットダウン時の電流は 0.5µA (標準値)であるため、LM27762はパワー・アンプ、 DACバイアスなど、大電流で低ノイズの負電圧を必要とす る用途で、理想的な性能を発揮します。このデバイスは、 必要な外付け部品もわずかで、サイズの小さなソリューショ ンを実現できます。

**負の電圧は、レギュレートされた反転チャージ・ポンプと、** それに続く低ノイズの負のLDOによって生成されます。 LM27762デバイスの反転チャージ・ポンプは2MHz (標準 値)のスイッチング周波数で動作するため、出力抵抗と電 圧リップルが減少します。正の電圧は、低ノイズの正の LDOを使用して、入力から生成されます。

LM27762の正と負の出力には、それぞれ専用のイネーブ ル入力があります。これらの出力は、システム固有の電源 シーケンス要件に対応するため、正と負のレールについ て、それぞれ独立したタイミングをサポートしています。イ ネーブル入力を互いに短絡させ、入力電圧へ接続するこ ともできます。LM27762には、オプションのパワー・グッド 機能があります。

#### 製品情報<sup>(1)</sup>

| 型番      | パッケージ     | 本体サイズ(公称)     |

|---------|-----------|---------------|

| LM27762 | WSON (12) | 2.00mm×3.00mm |

(1) 提供されているすべてのパッケージについては、このデータシート の末尾にある注文情報を参照してください。

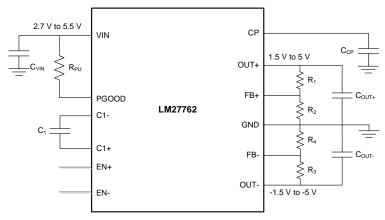

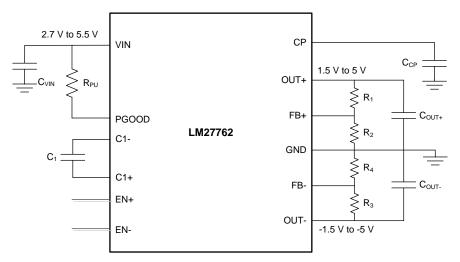

#### 概略回路図

Copyright © 2016, Texas Instruments Incorporated

|   | •   |

|---|-----|

| н | 777 |

|   | //  |

| 1 | 特長1                                  | 7.4 Device Functional Modes11     |

|---|--------------------------------------|-----------------------------------|

| 2 | アプリケーション                             | 8 Application and Implementation  |

| 3 | 概要1                                  | 8.1 Application Information       |

| 4 | 改訂履歴2                                | 8.2 Typical Application           |

| 5 | Pin Configuration and Functions      | 9 Power Supply Recommendations 17 |

| 6 | Specifications4                      | 10 Layout 17                      |

| • | 6.1 Absolute Maximum Ratings 4       | 10.1 Layout Guidelines 17         |

|   | 6.2 ESD Ratings                      | 10.2 Layout Example18             |

|   | 6.3 Recommended Operating Conditions | 11 デバイスおよびドキュメントのサポート             |

|   | 6.4 Thermal Information              | 11.1 デバイス・サポート19                  |

|   | 6.5 Electrical Characteristics       | 11.2 ドキュメントの更新通知を受け取る方法           |

|   | 6.6 Typical Characteristics          | 11.3 コミュニティ・リソース19                |

| 7 | Detailed Description 8               | 11.4 商標19                         |

| - | 7.1 Overview 8                       | 11.5 静電気放電に関する注意事項                |

|   | 7.2 Functional Block Diagram9        | 11.6 Glossary19                   |

|   | 7.3 Feature Description              | 12 メカニカル、パッケージ、および注文情報            |

# 4 改訂履歴

資料番号末尾の英字は改訂を表しています。その改訂履歴は英語版に準じています。

# Revision A (September 2016) から Revision B に変更 • WEBENCHのulinksを 追加 1 2016年7月発行のものから更新 Page • タイトルの「スイッチト・キャパシタ」を「チャージ・ポンプ」へ 変更 1 • 「特長」で「±1.5V~±5Vの低ノイズの可変の正および負の電源電圧を生成」を「可変の正電源電圧 (1.5V~5V) と、負電源電圧 (-1.5V~-5V) を低ノイズで生成」へ 変更 1

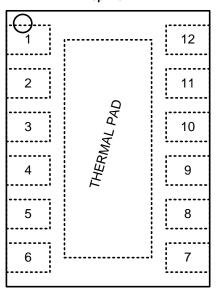

# **5 Pin Configuration and Functions**

DSS Package 12-Pin WSON With Thermal Pad Top View

# **Pin Functions**

| PIN         |        | TVDE   | DESCRIPTION                                                                                                        |

|-------------|--------|--------|--------------------------------------------------------------------------------------------------------------------|

| NAME        | NUMBER | TYPE   | DESCRIPTION                                                                                                        |

| C1+         | 10     | Power  | Positive terminal for C <sub>1</sub>                                                                               |

| C1-         | 9      | Power  | Negative terminal for C <sub>1</sub>                                                                               |

| CP          | 5      | Power  | Negative unregulated output voltage                                                                                |

| EN+         | 12     | Input  | Enable input for the positive LDO, Active high                                                                     |

| EN-         | 8      | Input  | Enable input for the charge pump and negative LDO, Active high                                                     |

| FB+         | 2      | Power  | Feedback input. Connect FB+ to an external resistor divider between OUT+ and GND. <b>DO NOT</b> leave unconnected. |

| FB-         | 7      | Power  | Feedback input. Connect FB– to an external resistor divider between OUT– and GND. <b>DO NOT</b> leave unconnected. |

| GND         | 4      | Ground | Ground                                                                                                             |

| OUT+        | 11     | Power  | Regulated positive output voltage                                                                                  |

| OUT-        | 6      | Power  | Regulated negative output voltage                                                                                  |

| PGOOD       | 1      | Output | Power Good flag; open drain; Logic 0 = power good, Logic 1 = power not good. Connect to ground if not used.        |

| VIN         | 3      | Power  | Positive power supply input                                                                                        |

| Thermal Pad | _      | Ground | Ground. DO NOT leave unconnected.                                                                                  |

# 6 Specifications

## 6.1 Absolute Maximum Ratings

over operating free-air temperature range (unless otherwise noted) (1)(2)

|                                                         | MIN                                        | MAX             | UNIT |

|---------------------------------------------------------|--------------------------------------------|-----------------|------|

| VIN to GND or GND to VOUT                               |                                            | 5.8             | V    |

| EN+, EN-                                                | GND - 0.3                                  | V <sub>IN</sub> | V    |

| CPOUT, OUT+ and OUT-, continuous output current         |                                            | 300             | mA   |

| OUT+, OUT- short-circuit duration to GND <sup>(3)</sup> |                                            | 1               | s    |

| Continuous power dissipation <sup>(4)</sup>             | sipation <sup>(4)</sup> Internally limited |                 |      |

| $T_{JMAX}^{(4)}$                                        |                                            | 150             | °C   |

| Operating input voltage, V <sub>IN</sub>                | 2.7                                        | 5.5             | V    |

| Operating output current, I <sub>OUT</sub>              | 0                                          | 250             | mA   |

| Operating ambient temperature, T <sub>A</sub>           | -40                                        | 85              | °C   |

| Operating junction temperature, T <sub>J</sub>          | -40                                        | 125             | °C   |

| Storage temperature, T <sub>stq</sub>                   | <b>–65</b>                                 | 150             | °C   |

<sup>(1)</sup> Stresses beyond those listed under Absolute Maximum Ratings may cause permanent damage to the device. These are stress ratings only, which do not imply functional operation of the device at these or any other conditions beyond those indicated under Recommended Operating Conditions. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

- (2) If Military/Aerospace specified devices are required, contact the TI Sales Office/Distributors for availability and specifications.

- (3) OUT may be shorted to GND for one second without damage. However, shorting OUT to VIN may damage the device and must be avoided. Also, for temperatures above T<sub>A</sub> = 85°C, V<sub>OUT</sub> must not be shorted to GND or VIN or device may be damaged.

- (4) Internal thermal shutdown circuitry protects the device from damage.

# 6.2 ESD Ratings

|                    |                         |                                                                     | VALUE | UNIT |

|--------------------|-------------------------|---------------------------------------------------------------------|-------|------|

| V                  | Flactroatatic disaboras | Human-body model (HBM), per ANSI/ESDA/JEDEC JS-001 <sup>(1)</sup>   | ±1000 | V    |

| V <sub>(ESD)</sub> | Electrostatic discharge | Charged-device model (CDM), per JEDEC specification JESD22-C101 (2) | ±250  | V    |

<sup>(1)</sup> JEDEC document JEP155 states that 500-V HBM allows safe manufacturing with a standard ESD control process.

#### 6.3 Recommended Operating Conditions

over operating free-air temperature range (unless otherwise noted)

|                                                | MIN | MAX | UNIT |

|------------------------------------------------|-----|-----|------|

| Operating ambient temperature, T <sub>A</sub>  | -40 | 85  | °C   |

| Operating junction temperature, T <sub>J</sub> | -40 | 125 | °C   |

#### 6.4 Thermal Information

|                       |                                              | LM27762    |      |  |

|-----------------------|----------------------------------------------|------------|------|--|

|                       | THERMAL METRIC <sup>(1)</sup>                | DSS (WSON) | UNIT |  |

|                       |                                              | 12 PINS    |      |  |

| $R_{\theta JA}$       | Junction-to-ambient thermal resistance       | 62.2       | °C/W |  |

| $R_{\theta JC(top)}$  | Junction-to-case (top) thermal resistance    | 54.7       | °C/W |  |

| $R_{\theta JB}$       | Junction-to-board thermal resistance         | 25.6       | °C/W |  |

| <b>У</b> ЈТ           | Junction-to-top characterization parameter   | 1.8        | °C/W |  |

| √<br>ЈВ               | Junction-to-board characterization parameter | 25.6       | °C/W |  |

| R <sub>⊕JC(bot)</sub> | Junction-to-case (bottom) thermal resistance | 9.2        | °C/W |  |

| R <sub>⊕JC(bot)</sub> | Junction-to-case (bottom) thermal resistance | 9.2        |      |  |

<sup>(1)</sup> For more information about traditional and new thermal metrics, see Semiconductor and IC Package Thermal Metrics.

<sup>(2)</sup> JEDEC document JEP157 states that 250-V CDM allows safe manufacturing with a standard ESD control process.

# 6.5 Electrical Characteristics

Typical limits apply for  $T_A$  = 25°C; minimum and maximum limits apply over the full temperature range. Unless otherwise specified  $V_{IN}$  = 5 V,  $C_{IN}$  =  $C_{OUT_+}$  =  $C_{OUT_-}$  = 2.2  $\mu$ F,  $C_1$  = 1  $\mu$ F,  $C_{POUT}$  = 4.7  $\mu$ F.

| PARAMETER          |                                        | TEST CONDITIONS                                                                                | MIN    | TYP   | MAX    | UNIT          |

|--------------------|----------------------------------------|------------------------------------------------------------------------------------------------|--------|-------|--------|---------------|

| IQ                 | Supply current                         | Open circuit, no load, EN+, EN-<br>connected to VIN. (1)                                       |        | 390   |        | μΑ            |

| I <sub>SD</sub>    | Shutdown supply current                |                                                                                                |        | 0.5   | 5      | μΑ            |

| $f_{SW}$           | Switching frequency                    | V <sub>IN</sub> = 3.6 V                                                                        | 1.7    | 2     | 2.3    | MHz           |

| R <sub>NEG</sub>   | Output resistance to C <sub>POUT</sub> | V <sub>IN</sub> = 5.5 V, I <sub>L</sub> = 100 mA                                               |        | 2.5   |        | Ω             |

| V <sub>LDO</sub> - | LDO dropout voltage                    | I <sub>L</sub> = 100 mA, V <sub>OUT</sub> = −5 V                                               |        | 30    |        | mV            |

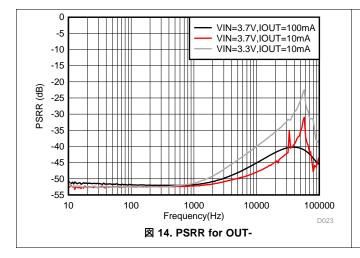

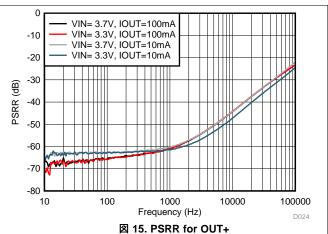

| PSRR               | Power supply rejection ratio, OUT-     | I <sub>L</sub> = 100 mA, V <sub>OUT</sub> = −1.8 V, 10 kHz                                     |        | 50    |        | dB            |

| V <sub>N</sub> -   | Output noise voltage                   | I <sub>L</sub> = 80 mA, 10 Hz to 100 kHz                                                       |        | 22    |        | $\mu V_{RMS}$ |

| $V_{FB-}$          | Feedback pin reference voltage         |                                                                                                | -1.238 | -1.22 | -1.202 | V             |

| V <sub>OUT</sub>   | Adjustable output voltage              | 5.5 V ≥ V <sub>IN</sub> ≥ 2.7 V                                                                | -5     |       | -1.5   | V             |

|                    | Load regulation                        | 0 to 250 mA, V <sub>OUT</sub> = -1.8 V                                                         |        | 34    |        | μV/mA         |

|                    | Line regulation                        | 5 V ≥ V <sub>IN</sub> ≥ 2.7 V, I <sub>L</sub> = 50 mA                                          |        | 1.5   |        | mV/V          |

| $V_{LDO+}$         | LDO dropout voltage                    | I <sub>L</sub> = 100 mA, V <sub>OUT</sub> = 5 V                                                |        | 45    |        | mV            |

| PSRR               | Power supply rejection ratio, OUT+     | I <sub>L</sub> = 100 mA, V <sub>OUT+</sub> = 1.8 V, 10 kHz                                     |        | 43    |        | dB            |

| V <sub>N+</sub>    | Output noise voltage                   | I <sub>L</sub> = 80 mA, 10 Hz to 100 kHz                                                       |        | 22    |        | $\mu V_{RMS}$ |

| V <sub>FB+</sub>   | Feedback pin reference voltage         |                                                                                                | 1.182  | 1.2   | 1.218  | V             |

|                    | Adjustable output voltage              | 5.5 V ≥ V <sub>IN</sub> ≥ 2.7 V                                                                | 1.5    |       | 5      | V             |

| V <sub>OUT+</sub>  | Load regulation                        | 0 to 250 mA, V <sub>OUT</sub> = 1.8 V                                                          |        | 11    |        | μV/mA         |

|                    | Line regulation                        | $5 \text{ V} \ge \text{V}_{\text{IN}} \ge 2.7 \text{ V}, \text{ I}_{\text{L}} = 50 \text{ mA}$ |        | 1.9   |        | mV/V          |

| V <sub>IH</sub>    | Enable pin input voltage high          | 5.5 V ≥ V <sub>IN</sub> ≥ 2.7 V                                                                | 1.2    |       |        | V             |

| V <sub>IL</sub>    | Enable pin input voltage low           | 5.5 V ≥ V <sub>IN</sub> ≥ 2.7 V                                                                |        |       | 0.4    | V             |

<sup>(1)</sup> When VIN = 5.5V charge pump may enter PWM mode in hot conditions.

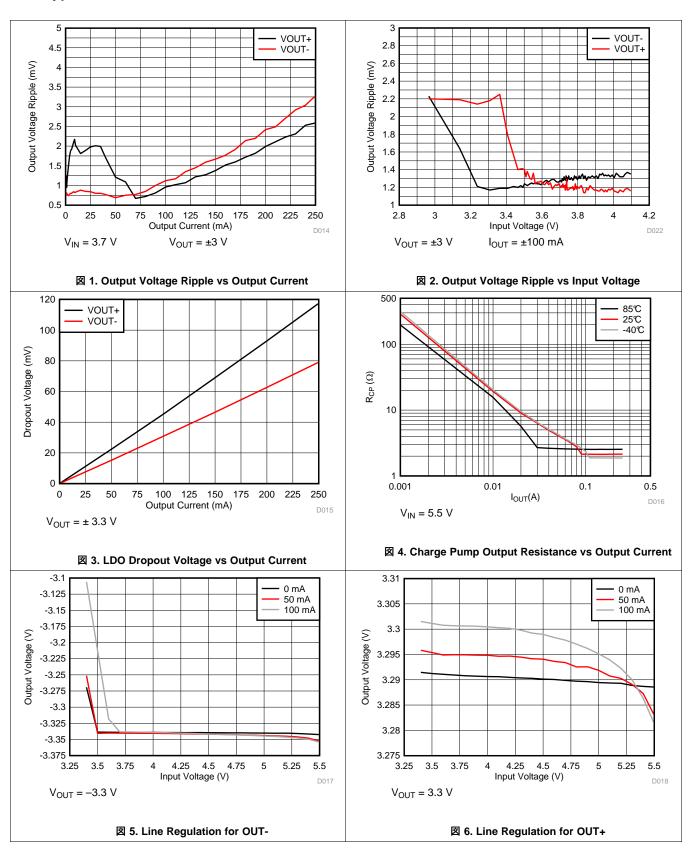

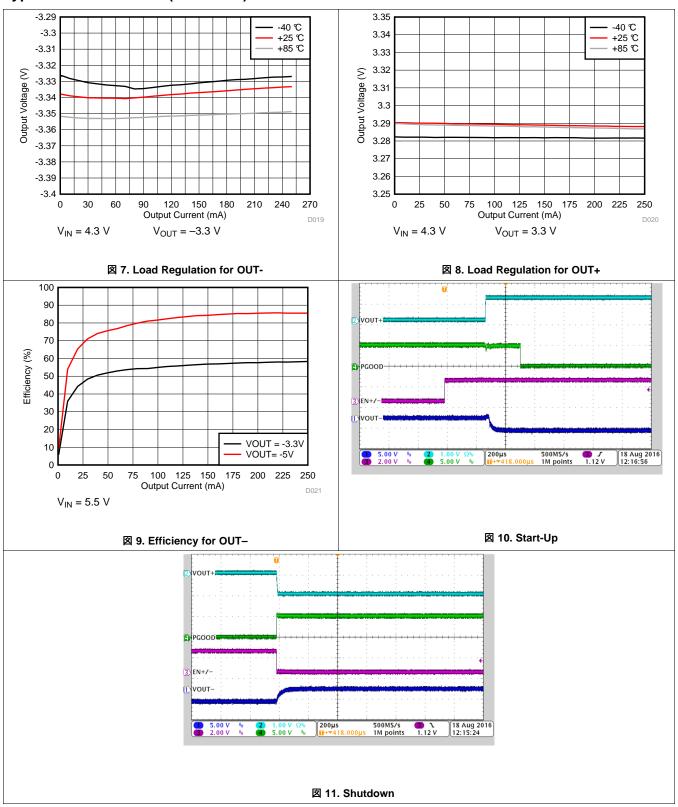

# 6.6 Typical Characteristics

# **Typical Characteristics (continued)**

# 7 Detailed Description

#### 7.1 Overview

The LM27762 low-noise inverting charge pump with both positive and negative LDOs delivers very low-noise adjustable positive and negative outputs between  $\pm 1.5$  V and  $\pm 5$  V. The output voltage levels of the positive and negative LDO are independently controllable with external resistors. Input voltage range of LM27762 is from 2.7 V to 5.5 V. Five low-cost capacitors are used in this circuit to provide up to  $\pm 250$  mA of output current. The LM27762 operates at 2-MHz (typical) switching frequency to reduce output resistance and voltage ripple. With an typical operating current of only 390  $\mu$ A and 0.5- $\mu$ A typical shutdown current, the LM27762 provides ideal performance for power amplifiers and DAC bias and other high-current, low-noise negative voltage needs.

The LM27762 device has an enable input (EN+) for the positive LDO and another enable input (EN-) for the negative charge pump and LDO. This supports independent timing for the positive and negative rails in system power sequence. Enable inputs can be also shorted together and connected to VIN. When LDO is disabled, output of the positive LDO has  $50\text{-k}\Omega$  pulldown to ground, and output of the negative LDO has  $50\text{-k}\Omega$  pullup to ground. The LM27762 has power good monitoring for OUT+ and OUT- outputs. The PGOOD pin is an opendrain output and requires an external pullup resistor. When Power Good feature is not used, PGOOD pin can be connected to ground.

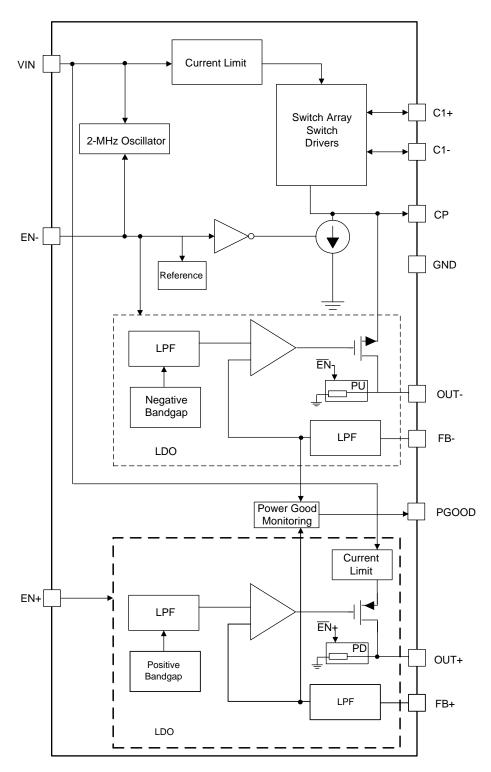

# 7.2 Functional Block Diagram

Copyright © 2016, Texas Instruments Incorporated

## 7.3 Feature Description

#### 7.3.1 Undervoltage Lockout

The LM27762 has an internal comparator that monitors the voltage at  $V_{IN}$  and forces the device into shutdown if the input voltage drops to 2.4 V. If the input voltage rises above 2.6 V, the LM27762 resumes normal operation.

#### 7.3.2 Input Current Limit

The LM27762 contains current limit circuitry that protects the device in the event of excessive input current and/or output shorts to ground. The charge pump and positive LDO both have 500 mA (typical) input current limit when the output is shorted directly to ground. When the LM27762 is current limiting, power dissipation in the device is likely to be quite high. In this event, thermal cycling is expected.

#### 7.3.3 PFM Operation

To minimize quiescent current during light load operation, the LM27762 allows PFM or pulse-skipping operation. By allowing the charge pump to switch less when the output current is low, the quiescent current drawn from the power source is minimized. The frequency of pulsed operation is not limited and can drop into the sub-2-kHz range when unloaded. As the load increases, the frequency of pulsing increases until it transitions to constant frequency. The fundamental switching frequency in the LM27762 is 2 MHz.

#### 7.3.4 Output Discharge

In shutdown, the LM27762 actively pulls down on the outputs (OUT+, OUT-) of the device until the output voltage reaches GND.

#### 7.3.5 Power Good Output (PGOOD)

The LM27762 has monitoring for the OUT+ and OUT- output voltage levels and open-drain PGOOD output.

| EN+  | EN-  | OUT+                  | OUT-                  | PGOOD |

|------|------|-----------------------|-----------------------|-------|

| Low  | Low  | Don't care            | Don't care H          |       |

| High | Low  | < 95% of target value | Don't care Hig        |       |

| High | Low  | > 95% of target value | Don't care            | Low   |

| Low  | High | Don't care            | < 95% of target value | High  |

| Low  | High | Don't care            | > 95% of target value | Low   |

| High | High | < 95% of target value | Don't care            | High  |

| High | High | Don't care            | < 95% of target value | High  |

| High | High | > 95% of target value | > 95% of target value | Low   |

表 1. PGOOD (Active Low) Operation

#### 7.3.6 Thermal Shutdown

The LM27762 implements a thermal shutdown mechanism to protect the device from damage due to overheating. When the junction temperature rises to 150°C (typical), the device switches into shutdown mode. The LM27762 releases thermal shutdown when the junction temperature is reduced to 130°C (typical).

Thermal shutdown is most often triggered by self-heating, which occurs when there is excessive power dissipation in the device and/or insufficient thermal dissipation. The LM27762 device power dissipation increases with increased output current and input voltage. When self-heating brings on thermal shutdown, thermal cycling is the typical result. Thermal cycling is the repeating process where the part self-heats, enters thermal shutdown (where internal power dissipation is practically zero), cools, turns on, and then heats up again to the thermal shutdown threshold. Thermal cycling is recognized by a pulsing output voltage and can be stopped by reducing the internal power dissipation (reduce input voltage and/or output current) or the ambient temperature. If thermal cycling occurs under desired operating conditions, thermal dissipation performance must be improved to accommodate the power dissipation of the device.

#### 7.4 Device Functional Modes

#### 7.4.1 Shutdown Mode

When enable pins (EN+, EN-) are low, both positive and negative outputs of LM27762 are disabled, and the device is in shutdown mode reducing the quiescent current to minimum level. In shutdown, the outputs of the LM27762 are pulled to ground (internal 50 k $\Omega$  between each OUT pin and ground).

#### 7.4.2 Enable Mode

Applying a voltage greater than 1.2 V to the EN+ pin enables the positive LDO. Applying a voltage greater than 1.2 V to the EN- pin enables the negative CP and LDO. When enabled, the positive and negative output voltages are equal to levels set by external resistors. Care must be taken to both the positive LDO and the inverting charge pump followed by negative LDO have enough headroom. Power Good ouput PGOOD indicates the status of OUT+ and OUT- voltage levels.

# 8 Application and Implementation

注

Information in the following applications sections is not part of the TI component specification, and TI does not warrant its accuracy or completeness. TI's customers are responsible for determining suitability of components for their purposes. Customers should validate and test their design implementation to confirm system functionality.

# 8.1 Application Information

The LM27762 input voltage range is from 2.7 V to 5.5 V. The positive LDO provides a positive voltage configurable with external gain setting resistors  $R_1$ ,  $R_2$ . The low-noise charge-pump voltage converter inverts the input voltage V to a negative output voltage. Charge pump is followed by the negative LDO which regulates a negative output voltage configurable with external gain setting resistors  $R_3$ ,  $R_4$ . Output voltage range is  $\pm$  1.5 V to  $\pm$  5 V. When selecting input (VIN) and output (OUT+, OUT-) voltages ranges, headroom required by the charge pump and LDOs must to be considered. Charge-pump minimum headroom can be estimated based on the maximum load current and charge pump output resistance.

The device uses five low-cost capacitors to provide up to 250 mA of output current. The LM27762 operates at a 2-MHz oscillator frequency to reduce charge-pump output resistance and voltage ripple under heavy loads. When using the optional open-drain PGOOD feature, connect a 10-k $\Omega$  pullup resistor (R<sub>PU</sub>) to VIN. Connect pin to ground if PGOOD is not used.

# 8.2 Typical Application

Copyright © 2016, Texas Instruments Incorporated

図 12. LM27762 Typical Application

## **Typical Application (continued)**

#### 8.2.1 Design Requirements

The following example describes powering an amplifier driving high impedance headphones. Input voltage is from a smart-phone battery. Amplifier is driving  $2\text{-V}_{\text{RMS}}$  to  $600\text{-}\Omega$  stereo headphones.

| 表 2. Application | Example | Design | <b>Parameters</b> |

|------------------|---------|--------|-------------------|

|------------------|---------|--------|-------------------|

| DESIGN PARAMETER                                         | EXAMPLE VALUE                                                                |

|----------------------------------------------------------|------------------------------------------------------------------------------|

| Input voltage                                            | 3.3 V to 4.2 V                                                               |

| Output voltage                                           | ±3 V                                                                         |

| Output current                                           | 10 mA (LM27762 capability 250 mA maximum)                                    |

| C <sub>VIN</sub> , C <sub>OUT+</sub> , C <sub>OUT-</sub> | 2.2 μF                                                                       |

| C <sub>CP</sub>                                          | 4.7 μF                                                                       |

| R <sub>PU</sub>                                          | 10 k $\Omega$ (optional, connect PGOOD pin to ground if feature is not used) |

#### 8.2.2 Detailed Design Procedure

#### 8.2.2.1 Custom Design With WEBENCH® Tools

Click here to create a custom design using the LM27762 device with the WEBENCH® Power Designer.

- 1. Start by entering the input voltage (V<sub>IN</sub>), output voltage (V<sub>OUT</sub>), and output current (I<sub>OUT</sub>) requirements.

- 2. Optimize the design for key parameters such as efficiency, footprint, and cost using the optimizer dial.

- 3. Compare the generated design with other possible solutions from Texas Instruments.

The WEBENCH Power Designer provides a customized schematic along with a list of materials with real-time pricing and component availability.

In most cases, these actions are available:

- Run electrical simulations to see important waveforms and circuit performance.

- Run thermal simulations to understand board thermal performance.

- Export customized schematic and layout into popular CAD formats.

- Print PDF reports for the design, and share the design with colleagues.

Get more information about WEBENCH tools at www.ti.com/WEBENCH.

## 8.2.2.2 Positive Low-Dropout Linear Regulator and OUT+ Voltage Setting

LM27762 features a low-dropout, linear positive voltage regulator (LDO). The LDO output is rated for a current of 250 mA. This LDO allows the device to provide a very low noise output, low output voltage ripple, high PSRR, and low line or load transient response.

The positive output voltage of the LM27762 is externally configurable. The value of  $R_1$  and  $R_2$  determines the output voltage setting. The output voltage can be calculated using  $\pm 1$ :

$$V_{OUT} = 1.2 \text{ V} \times (R_1 + R_2) / R_2 \tag{1}$$

The value for  $R_2$  must be no less than 50 k $\Omega$ .

#### 8.2.2.3 Charge-Pump Voltage Inverter

The main application of the LM27762 is to generate a regulated negative supply voltage. The voltage inverter circuit uses only three external capacitors, and the LDO regulator circuit uses one additional output capacitor.

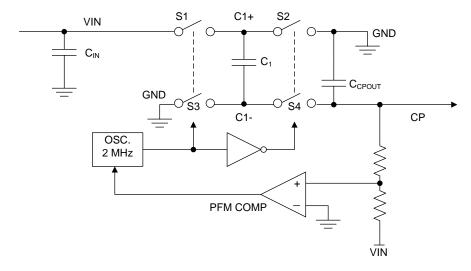

The voltage inverter portion of the LM27761 contains four large CMOS switches which are switched in sequence to invert the input supply voltage. Energy transfer and storage are provided by external capacitors.  $\boxtimes$  13 shows the voltage switches S2 and S4 are open. In the second time interval, S1 and S3 are open; at the same time, S2 and S4 are closed, and C<sub>1</sub> is charging C<sub>CP</sub>. After a number of cycles, the voltage across C<sub>CP</sub> is pumped into V<sub>IN</sub>. Because the anode of C<sub>CP</sub> is connected to ground, the output at the cathode of C<sub>CP</sub> equals  $-(V_{IN})$  when there is no load current. When a load is added, the output voltage drop is determined by the parasitic resistance (R<sub>DSON</sub> of the MOSFET switches and the equivalent series resistance (ESR) of the capacitors) and the charge transfer loss between the capacitors.

Copyright © 2016, Texas Instruments Incorporated

#### 図 13. Voltage Inverting Principle

The output characteristic of this circuit can be approximated by an ideal voltage source in series with a resistance. The voltage source equals  $-(V_{IN})$ . The output resistance  $R_{OUT}$  is a function of the ON resistance of the internal MOSFET switches, the oscillator frequency, the capacitance, and the ESR of  $C_1$  and  $C_{CP}$ . Because the switching current charging and discharging  $C_1$  is approximately twice as the output current, the effect of the ESR of the pumping capacitor  $C_1$  is multiplied by four in the output resistance. The charge-pump output capacitor  $C_{CP}$  is charging and discharging at a current approximately equal to the output current; therefore, its ESR only counts once in the output resistance. A good approximation of charge-pump  $R_{OUT}$  is shown in  $\vec{\pm}$  2:

$$R_{OUT} = (2 \times R_{SW}) + [1 / (f_{SW} \times C_1)] + (4 \times ESR_{C1}) + ESR_{CCP}$$

where

High capacitance and low-ESR ceramic capacitors reduce the output resistance.

#### 8.2.2.4 Negative Low-Dropout Linear Regulator and OUT- Voltage Setting

At the output of the inverting charge-pump the LM27762 features a low-dropout, linear negative voltage regulator (LDO). The LDO output is rated for a current of 250 mA. This negative LDO allows the device to provide a very low noise output, low output voltage ripple, high PSRR, and low line or load transient response.

The negative output voltage of the LM27762 is externally configurable. The value of  $R_3$  and  $R_4$  determines the output voltage setting. The output voltage can be calculated using  $\pm$  1:

$$V_{OIIT} = -1.22 \text{ V} \times (R_3 + R_4) / R_4$$

(3)

The value for  $R_4$  must be no less than 50 k $\Omega$ .

## 8.2.2.5 External Capacitor Selection

The LM27762 requires 5 external capacitors for proper operation. Surface-mount multi-layer ceramic capacitors are recommended. These capacitors are small, inexpensive, and have very low ESR ( $\leq$  15 m $\Omega$  typical). Tantalum capacitors, OS-CON capacitors, and aluminum electrolytic capacitors generally are not recommended for use with the LM27762 due to their high ESR compared to ceramic capacitors.

For most applications, ceramic capacitors with an X7R or X5R temperature characteristic are preferable for use with the LM27762. These capacitors have tight capacitance tolerances (as good as  $\pm 10\%$ ) and hold their value over temperature (X7R:  $\pm 15\%$  over -55°C to +125°C; X5R  $\pm 15\%$  over -55°C to +85°C).

Using capacitors with a Y5V or Z5U temperature characteristic is generally not recommended for the LM27762. These capacitors typically have wide capacitance tolerance (80%, ....20%) and vary significantly over temperature (Y5V: 22%, -82% over  $-30^{\circ}$ C to  $+85^{\circ}$ C range; Z5U: 22%, -56% over  $10^{\circ}$ C to  $85^{\circ}$ C range). Under some conditions a  $1-\mu$ F-rated Y5V or Z5U capacitor could have a capacitance as low as  $0.1~\mu$ F. Such detrimental deviation is likely to cause Y5V and Z5U capacitors to fail to meet the minimum capacitance requirements of the LM27762.

Net capacitance of a ceramic capacitor decreases with increased DC bias. This degradation can result in lower-than-expected capacitance on the input and/or output, resulting in higher ripple voltages and currents. Using capacitors at DC bias voltages significantly below the capacitor voltage rating usually minimizes DC bias effects. Consult capacitor manufacturers for information on capacitor DC bias characteristics.

Capacitance characteristics can vary quite dramatically with different application conditions, capacitor types, and capacitor manufacturers. TI strongly recommends that the LM27762 circuit be evaluated thoroughly early in the design-in process with the mass-production capacitor of choice. This helps ensure that any such variability in capacitance does not negatively impact circuit performance.

#### 8.2.2.5.1 Charge-Pump Output Capacitor

In typical applications, Texas Instruments recommends a  $4.7-\mu F$  low-ESR ceramic charge-pump output capacitor ( $C_{CP}$ ). Different output capacitance values can be used to reduce charge pump ripple, shrink the solution size, and/or cut the cost of the solution. However, changing the output capacitor may also require changing the flying capacitor or input capacitor to maintain good overall circuit performance.

In higher-current applications, a  $10-\mu F$ , 10-V low-ESR ceramic output capacitor is recommended. If a small output capacitor is used, the output ripple can become large during the transition between PFM mode and constant switching. To prevent toggling, a  $2-\mu F$  capacitance is recommended. For example,  $10-\mu F$ , 10-V output capacitor in a 0402 case size typically has only  $2-\mu F$  capacitance when biased to 5~V.

#### 8.2.2.5.2 Input Capacitor

The input capacitor (C2) is a reservoir of charge that aids in a quick transfer of charge from the supply to the flying capacitors during the charge phase of operation. The input capacitor helps to keep the input voltage from drooping at the start of the charge phase when the flying capacitors are connected to the input. It also filters noise on the input pin, keeping this noise out of the sensitive internal analog circuitry that is biased off the input line.

Input capacitance has a dominant and first-order effect on the input ripple magnitude. Increasing (decreasing) the input capacitance results in a proportional decrease (increase) in input voltage ripple. Input voltage, output current, and flying capacitance also affects input ripple levels to some degree.

In typical applications, a  $4.7-\mu F$  low-ESR ceramic capacitor is recommended on the input. When operating near the maximum load of 250 mA, after taking into the DC bias derating, a minimum recommended input capacitance is 2  $\mu F$  or larger. Different input capacitance values can be used to reduce ripple, shrink the solution size, and/or cut the cost of the solution.

#### 8.2.2.5.3 Flying Capacitor

The flying capacitor ( $C_1$ ) transfers charge from the input to the output. Flying capacitance can impact both output current capability and ripple magnitudes. If flying capacitance is too small, the LM27762 may not be able to regulate the output voltage when load currents are high. On the other hand, if the flying capacitance is too large, the flying capacitor might overwhelm the input and charge pump output capacitors, resulting in increased input and output ripple.

In typical high-current applications,  $0.47-\mu F$  or  $1-\mu F$  10-V low-ESR ceramic capacitors are recommended for the flying capacitors. Polarized capacitors (tantalum, aluminum, electrolytic, etc.) must not be used for the flying capacitor, as they could become reverse-biased during LM27762 operation.

#### 8.2.2.5.4 LDO Output Capacitor

The LDO output capacitor (COUT+, COUT-) value and the ESR affect stability, output ripple, output noise, PSRR and transient response. The LM27762 only requires the use of a 2.2-µF ceramic output capacitor for stable operation. For typical applications, a 2.2-µF ceramic output capacitor located close to the output is sufficient.

#### 8.2.2.6 Power Dissipation

The allowed power dissipation for any package is a measure of the ability of the device to pass heat from the junctions of the device to the heatsink and the ambient environment. Thus, the power dissipation is dependent on the ambient temperature and the thermal resistance across the various interfaces between the die junction and ambient air.

The maximum allowable power dissipation can be calculated by 式 4:

$$P_{D-MAX} = (T_{J-MAX} - T_A) / R_{\theta JA}$$

(4)

The actual power being dissipated in the device can be represented by 式 5:

$$P_{D} = P_{IN} - P_{OUT} = V_{IN} \times (-I_{OUT-} + I_{OUT+} + I_{Q}) - (V_{OUT+} \times I_{OUT-} + V_{OUT-} \times I_{OUT-})$$

(5)

式 4 and 式 5 establish the relationship between the maximum power dissipation allowed due to thermal consideration, the voltage drop across the device, and the continuous current capability of the device. These equations must be used to determine the optimum operating conditions for the device in a given application.

In lower power dissipation applications the maximum ambient temperature ( $T_{A-MAX}$ ) may be increased. In higher power dissipation applications the maximum ambient temperature( $T_{A-MAX}$ ) may have to be derated.  $T_{A-MAX}$  can be calculated using  $\pm$  6:

$$T_{A-MAX} = T_{J-MAX-OP} - (R_{\theta JA} \times P_{D-MAX})$$

where

- T<sub>J-MAX-OP</sub> = maximum operating junction temperature (125°C)

- P<sub>D-MAX</sub> = the maximum allowable power dissipation

- R<sub>θ,IA</sub> = junction-to-ambient thermal resistance of the package

(6)

Alternately, if  $T_{A-MAX}$  cannot be derated, the power dissipation value must be reduced. This can be accomplished by reducing the input voltage as long as the minimum  $V_{IN}$  is not violated, or by reducing the output current, or some combination of the two.

#### 8.2.3 Application Curves

Refer also to Typical Characteristics

# 9 Power Supply Recommendations

The LM27762 is designed to operate from an input voltage supply range between 2.7 V and 5.5 V. This input supply must be well regulated and capable of supplying the required input current. If the input supply is located far from the LM27762, additional bulk capacitance may be required in addition to the ceramic bypass capacitors.

# 10 Layout

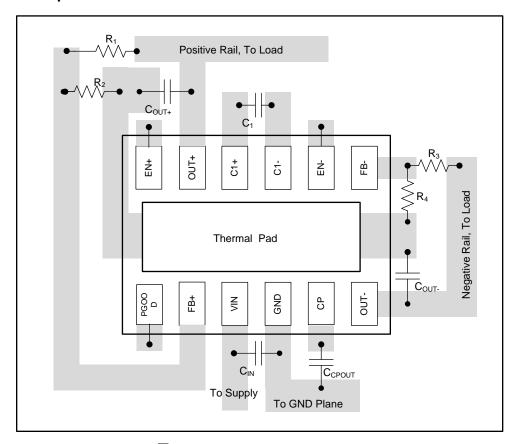

#### 10.1 Layout Guidelines

The high switching frequency and large switching currents of the LM27762 make the choice of layout important. Use the following steps as a reference to ensure the device is stable and maintains proper LED current regulation across its intended operating voltage and current range:

- Place C<sub>IN</sub> on the top layer (same layer as the LM27762) and as close as possible to the device. Connecting

the input capacitor through short, wide traces to both the VIN and GND pins reduces the inductive voltage

spikes that occur during switching, which can corrupt the VIN line.

- Place C<sub>CPOUT</sub> on the top layer (same layer as the LM27762) and as close as possible to the VOUT and GND pins. The returns for both C<sub>IN</sub> and C<sub>CPOUT</sub> must come together at one point, as close as possible to the GND pin. Connecting C<sub>CPOUT</sub> through short, wide traces reduces the series inductance on the VCPOUT and GND pins that can corrupt the VCPOUT and GND lines and cause excessive noise in the device and surrounding circuitry.

- Place C<sub>1</sub> on top layer (same layer as the LM27762) and as close as possible to the device. Connect the flying

capacitor through short, wide traces to both the C1+ and C1- pins.

- Place C<sub>OUT+</sub>, C<sub>OUT-</sub> on the top layer (same layer as the LM27762) and as close to the respective OUT pin as

possible. For best performance the ground connection for C<sub>OUT</sub> must connect back to the GND connection at

the thermal pad of the device.

- Place R<sub>1</sub> to R<sub>4</sub> on the top layer (same layer as LM27762) and as close as possible to the respective FB pin.

For best performance the ground connection of R<sub>2</sub>, R<sub>4</sub> must connect back to the GND connection at the thermal pad of the device.

Connections using long trace lengths, narrow trace widths, or connections through vias must be avoided. These add parasitic inductance and resistance that results in inferior performance, especially during transient conditions.

# 10.2 Layout Example

図 16. LM27762 Layout Example (Note: Pullup resistor for PGOOD not shown in example.)

# 11 デバイスおよびドキュメントのサポート

#### 11.1 デバイス・サポート

• 『LM27762EVM評価モジュールの使用法』

#### 11.1.1 開発サポート

#### 11.1.1.1 WEBENCH®ツールによるカスタム設計

ここをクリックすると、WEBENCH® Power Designerにより、LM27762デバイスを使用するカスタム設計を作成できます。

- 1. 最初に、入力電圧(V<sub>IN</sub>)、出力電圧(V<sub>OUT</sub>)、出力電流(I<sub>OUT</sub>)の要件を入力します。

- 2. オプティマイザのダイヤルを使用して、効率、占有面積、コストなどの主要なパラメータについて設計を最適化します。

- 3. 生成された設計を、テキサス・インスツルメンツが提供する他のソリューションと比較します。

WEBENCH Power Designerでは、カスタマイズされた回路図と部品リストを、リアルタイムの価格と部品の在庫情報と併せて参照できます。

ほとんどの場合、次の操作を実行可能です。

- 電気的なシミュレーションを実行し、重要な波形と回路の性能を確認する。

- 熱シミュレーションを実行し、基板の熱特性を把握する。

- カスタマイズされた回路図やレイアウトを、一般的なCADフォーマットでエクスポートする。

- 設計のレポートをPDFで印刷し、同僚と設計を共有する。

WEBENCHツールの詳細は、www.ti.com/WEBENCHでご覧になれます。

# 11.2 ドキュメントの更新通知を受け取る方法

ドキュメントの更新についての通知を受け取るには、ti.comのデバイス製品フォルダを開いてください。右上の隅にある「通知を受け取る」をクリックして登録すると、変更されたすべての製品情報に関するダイジェストを毎週受け取れます。変更の詳細については、修正されたドキュメントに含まれている改訂履歴をご覧ください。

#### 11.3 コミュニティ・リソース

The following links connect to TI community resources. Linked contents are provided "AS IS" by the respective contributors. They do not constitute TI specifications and do not necessarily reflect TI's views; see TI's Terms of Use.

TI E2E™オンライン・コミュニティ *TIのE2E(Engineer-to-Engineer)コミュニティ。*エンジニア間の共同作業を促進するために開設されたものです。e2e.ti.comでは、他のエンジニアに質問し、知識を共有し、アイディアを検討して、問題解決に役立てることができます。

設計サポート *TIの設計サポート* 役に立つE2Eフォーラムや、設計サポート・ツールをすばやく見つけることができます。技術サポート用の連絡先情報も参照できます。

#### 11.4 商標

E2E is a trademark of Texas Instruments.

WEBENCH is a registered trademark of Texas Instruments.

All other trademarks are the property of their respective owners.

#### 11.5 静電気放電に関する注意事項

これらのデバイスは、限定的なESD(静電破壊)保護機能を内蔵しています。保存時または取り扱い時は、MOSゲートに対する静電破壊を防止するために、リード線同士をショートさせておくか、デバイスを導電フォームに入れる必要があります。

#### 11.6 Glossary

SLYZ022 — TI Glossary.

This glossary lists and explains terms, acronyms, and definitions.

# 12 メカニカル、パッケージ、および注文情報

以降のページには、メカニカル、パッケージ、および注文に関する情報が記載されています。この情報は、そのデバイスについて利用可能な最新のデータです。このデータは予告なく変更されることがあり、ドキュメントが改訂される場合もあります。本データシートのブラウザ版を使用されている場合は、画面左側の説明をご覧ください。

www.ti.com 28-Sep-2021

#### **PACKAGING INFORMATION**

| Orderable Device | Status | Package Type | Package<br>Drawing | Pins | Package<br>Qty | Eco Plan     | Lead finish/<br>Ball material | MSL Peak Temp      | Op Temp (°C) | Device Marking<br>(4/5) | Samples |

|------------------|--------|--------------|--------------------|------|----------------|--------------|-------------------------------|--------------------|--------------|-------------------------|---------|

| LM27762DSSR      | ACTIVE | WSON         | DSS                | 12   | 3000           | RoHS & Green | NIPDAU                        | Level-1-260C-UNLIM | -40 to 85    | L27762                  | Samples |

| LM27762DSST      | ACTIVE | WSON         | DSS                | 12   | 250            | RoHS & Green | NIPDAU                        | Level-1-260C-UNLIM | -40 to 85    | L27762                  | Samples |

(1) The marketing status values are defined as follows:

**ACTIVE:** Product device recommended for new designs.

LIFEBUY: TI has announced that the device will be discontinued, and a lifetime-buy period is in effect.

NRND: Not recommended for new designs. Device is in production to support existing customers, but TI does not recommend using this part in a new design.

PREVIEW: Device has been announced but is not in production. Samples may or may not be available.

**OBSOLETE:** TI has discontinued the production of the device.

(2) RoHS: TI defines "RoHS" to mean semiconductor products that are compliant with the current EU RoHS requirements for all 10 RoHS substances, including the requirement that RoHS substance do not exceed 0.1% by weight in homogeneous materials. Where designed to be soldered at high temperatures, "RoHS" products are suitable for use in specified lead-free processes. TI may reference these types of products as "Pb-Free".

RoHS Exempt: TI defines "RoHS Exempt" to mean products that contain lead but are compliant with EU RoHS pursuant to a specific EU RoHS exemption.

Green: TI defines "Green" to mean the content of Chlorine (CI) and Bromine (Br) based flame retardants meet JS709B low halogen requirements of <=1000ppm threshold. Antimony trioxide based flame retardants must also meet the <=1000ppm threshold requirement.

- (3) MSL, Peak Temp. The Moisture Sensitivity Level rating according to the JEDEC industry standard classifications, and peak solder temperature.

- (4) There may be additional marking, which relates to the logo, the lot trace code information, or the environmental category on the device.

- (5) Multiple Device Markings will be inside parentheses. Only one Device Marking contained in parentheses and separated by a "~" will appear on a device. If a line is indented then it is a continuation of the previous line and the two combined represent the entire Device Marking for that device.

- (6) Lead finish/Ball material Orderable Devices may have multiple material finish options. Finish options are separated by a vertical ruled line. Lead finish/Ball material values may wrap to two lines if the finish value exceeds the maximum column width.

**Important Information and Disclaimer:** The information provided on this page represents TI's knowledge and belief as of the date that it is provided. TI bases its knowledge and belief on information provided by third parties, and makes no representation or warranty as to the accuracy of such information. Efforts are underway to better integrate information from third parties. TI has taken and continues to take reasonable steps to provide representative and accurate information but may not have conducted destructive testing or chemical analysis on incoming materials and chemicals. TI and TI suppliers consider certain information to be proprietary, and thus CAS numbers and other limited information may not be available for release.

In no event shall TI's liability arising out of such information exceed the total purchase price of the TI part(s) at issue in this document sold by TI to Customer on an annual basis.

# **PACKAGE OPTION ADDENDUM**

www.ti.com 28-Sep-2021

# PACKAGE MATERIALS INFORMATION

www.ti.com 9-Mar-2017

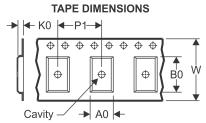

# TAPE AND REEL INFORMATION

| A0 | Dimension designed to accommodate the component width     |

|----|-----------------------------------------------------------|

| B0 | Dimension designed to accommodate the component length    |

| K0 | Dimension designed to accommodate the component thickness |

| W  | Overall width of the carrier tape                         |

| P1 | Pitch between successive cavity centers                   |

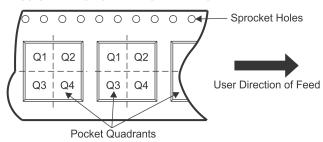

# QUADRANT ASSIGNMENTS FOR PIN 1 ORIENTATION IN TAPE

#### \*All dimensions are nominal

| Device      | Package<br>Type | Package<br>Drawing |    | SPQ  | Reel<br>Diameter<br>(mm) | Reel<br>Width<br>W1 (mm) | A0<br>(mm) | B0<br>(mm) | K0<br>(mm) | P1<br>(mm) | W<br>(mm) | Pin1<br>Quadrant |

|-------------|-----------------|--------------------|----|------|--------------------------|--------------------------|------------|------------|------------|------------|-----------|------------------|

| LM27762DSSR | WSON            | DSS                | 12 | 3000 | 180.0                    | 8.4                      | 2.25       | 3.25       | 1.05       | 4.0        | 8.0       | Q1               |

| LM27762DSST | WSON            | DSS                | 12 | 250  | 180.0                    | 8.4                      | 2.25       | 3.25       | 1.05       | 4.0        | 8.0       | Q1               |

www.ti.com 9-Mar-2017

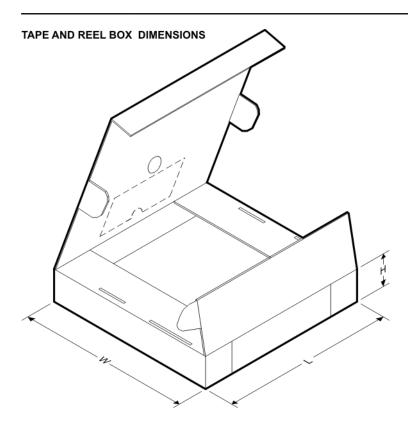

#### \*All dimensions are nominal

| Device      | Package Type | Package Drawing | Pins | SPQ  | Length (mm) | Width (mm) | Height (mm) |

|-------------|--------------|-----------------|------|------|-------------|------------|-------------|

| LM27762DSSR | WSON         | DSS             | 12   | 3000 | 210.0       | 185.0      | 35.0        |

| LM27762DSST | WSON         | DSS             | 12   | 250  | 210.0       | 185.0      | 35.0        |

Images above are just a representation of the package family, actual package may vary. Refer to the product data sheet for package details.

4209244/D

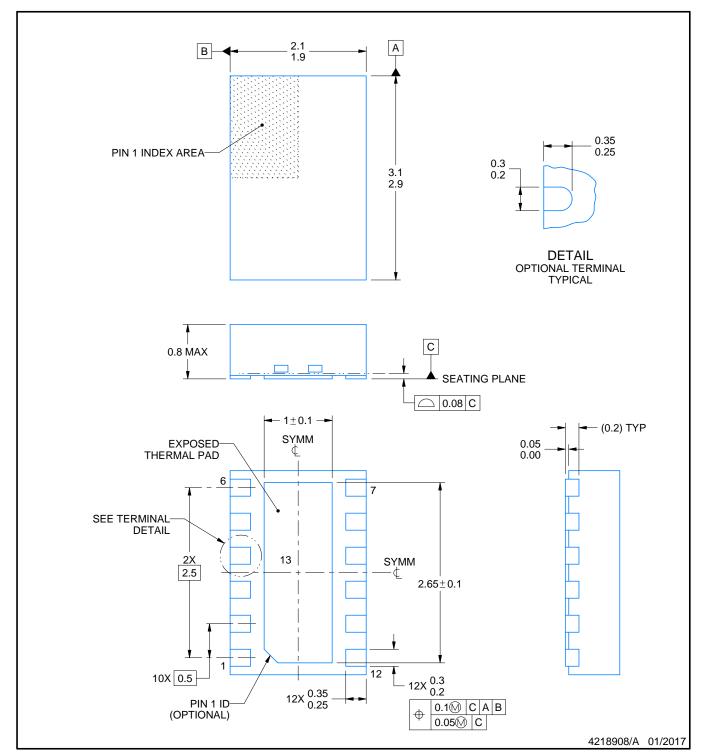

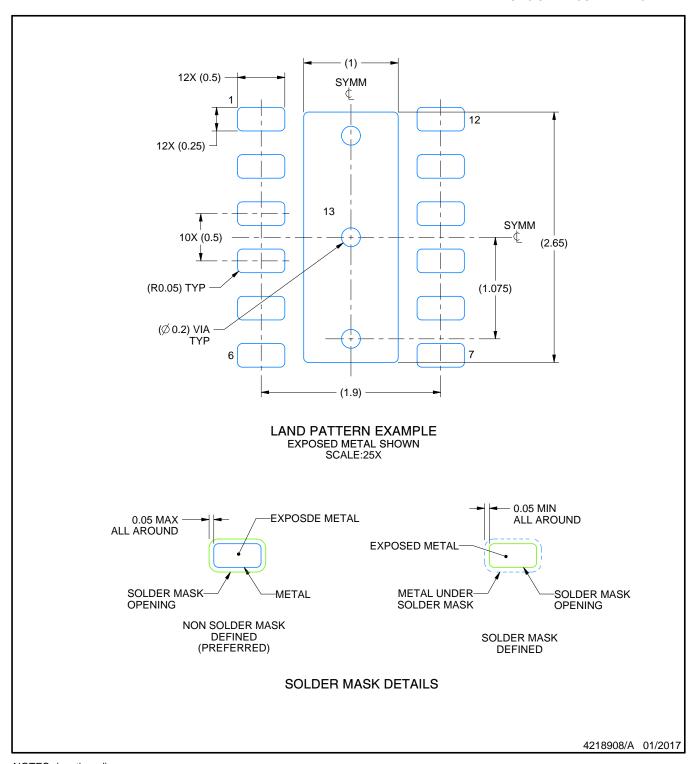

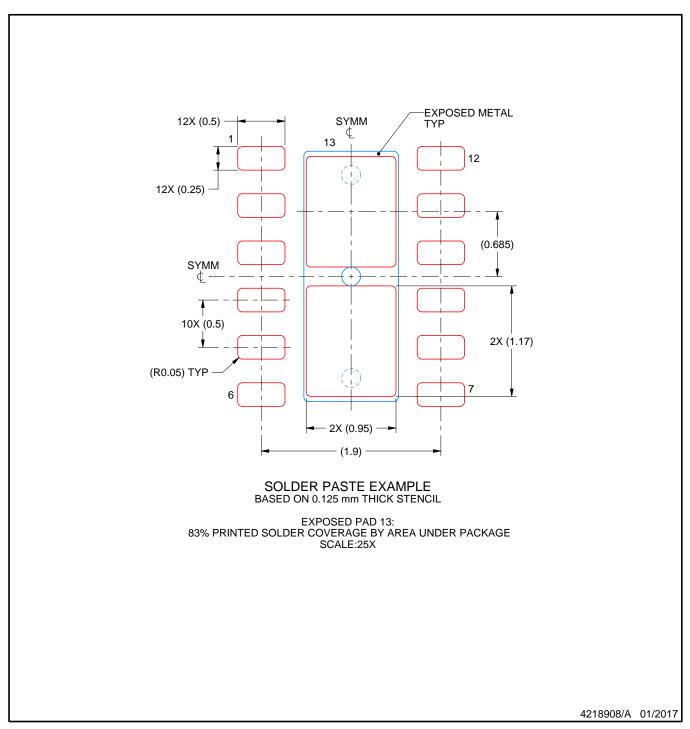

PLASTIC SMALL OUTLINE - NO LEAD

#### NOTES:

- 1. All linear dimensions are in millimeters. Any dimensions in parenthesis are for reference only. Dimensioning and tolerancing per ASME Y14.5M.

2. This drawing is subject to change without notice.

- 3. The package thermal pad must be soldered to the printed circuit board for optimal thermal and mechanical performance.

PLASTIC SMALL OUTLINE - NO LEAD

NOTES: (continued)

- 4. This package is designed to be soldered to a thermal pad on the board. For more information, see Texas Instruments literature number SLUA271 (www.ti.com/lit/slua271).

- 5. Vias are optional depending on application, refer to device data sheet. If any vias are implemented, refer to their locations shown on this view. It is recommended that vias under paste be filled, plugged or tented.

PLASTIC SMALL OUTLINE - NO LEAD

NOTES: (continued)

6. Laser cutting apertures with trapezoidal walls and rounded corners may offer better paste release. IPC-7525 may have alternate design recommendations.

# 重要なお知らせと免責事項

TI は、技術データと信頼性データ (データシートを含みます)、設計リソース (リファレンス・デザインを含みます)、アプリケーションや設計に関する各種アドバイス、Web ツール、安全性情報、その他のリソースを、欠陥が存在する可能性のある「現状のまま」提供しており、商品性および特定目的に対する適合性の黙示保証、第三者の知的財産権の非侵害保証を含むいかなる保証も、明示的または黙示的にかかわらず拒否します。

これらのリソースは、TI 製品を使用する設計の経験を積んだ開発者への提供を意図したものです。(1) お客様のアプリケーションに適した TI 製品の選定、(2) お客様のアプリケーションの設計、検証、試験、(3) お客様のアプリケーションが適用される各種規格や、その他のあらゆる安全性、セキュリティ、またはその他の要件を満たしていることを確実にする責任を、お客様のみが単独で負うものとします。上記の各種リソースは、予告なく変更される可能性があります。これらのリソースは、リソースで説明されている TI 製品を使用するアプリケーションの開発の目的でのみ、TI はその使用をお客様に許諾します。これらのリソースに関して、他の目的で複製することや掲載することは禁止されています。TI や第三者の知的財産権のライセンスが付与されている訳ではありません。お客様は、これらのリソースを自身で使用した結果発生するあらゆる申し立て、損害、費用、損失、責任について、TI およびその代理人を完全に補償するものとし、TI は一切の責任を拒否します。

TI の製品は、TI の販売約款 (https://www.tij.co.jp/ja-jp/legal/terms-of-sale.html)、または ti.com やかかる TI 製品の関連資料などのいずれかを通じて提供する適用可能な条項の下で提供されています。TI がこれらのリソースを提供することは、適用される TI の保証または他の保証の放棄の拡大や変更を意味するものではありません。

日本語版 日本テキサス・インスツルメンツ合同会社 Copyright © 2021, Texas Instruments Incorporated